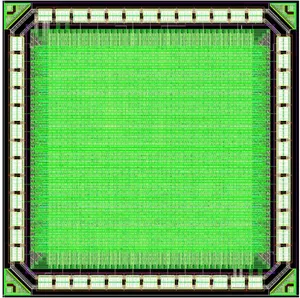

TACO: A Tiled Architecture of (re)Configurable Operators

TACO is a custom tiled FPGA architecture with the goal of delivering a fully programmable reconfigurable fabric along with an end-to-end toolchain for compilation and deployment. The chip integrates 288 configurable logic blocks arranged in an 18×17 fabric, 8-wide programmable interconnect through switch boxes and connection boxes, 1 KB of on-chip BRAM, 9 dedicated MAC units for arithmetic acceleration, 39 GPIO pins, JTAG-based programming/debug support, and 64 selectable clock frequencies via a programmable divider. Additionally, we built a Verilog-to-bitstream flow using tools such as Yosys and VTR/VPR with custom scripts to generate architecture-compatible bitstreams.