NOTE: For those of you who read through the ECE512 simulator hints page posted here earlier, a few key differences are listed below:

The rename and scheduler stages are implementations of

(derived from) virtual base classes defined in

The ECE511 simulator does not perform renaming. The rename stage is a 'dummy' placeholder stage which would be later used for plugging in your code in a later MP

The ECE511 simulator can switch between using an in-order scheduler (default option) or an out-of-order (OoO) scheduler using the commandline flag -ooo_scheduler. The relevance of this functionality would be clear during a later MP.

The ECE511 simulator does not have a branch predictor.

Functional Basics: Read the circuit class tutorial. This will help you figure out how the various stages are put together and how to make use of the inports and stateregs.

Simulator ISA Reference Manual: The simulator is based on a modified MIPS 64bit instruction set... and knowing the varieties of branch, memory etc. instructions is sometimes necessary to figure out corner cases.

High level view: Refer to the pipeline stage defs in main() in pipelined_model.cc to understand how the stages are connected (using attach method calls) to each other.

Stage level view: Each stage maintains some state (its private members) and has a few inputs (inports) and outputs (stateregs) defined in its header. Trace through the operations being performed on these in the recalc method to understand how a stage operates

Signal level view: Look at the source of a particular signal and then trace the way to all the stages it is attached to. Mostly a lot of code browsing.

Superpipelined: The simulator models a one wide processor which is then used to approximate the performance of an equivalent 'w' wide processor by adding additional frontend delay (to simulate misprediction penalty) and by factoring in the width in various stat calculations

[vdhar2@localhost ece511-sim]$ tree . |-- Makefile (simulator build file) |-- apps (a few selected spec2000 benckmarks) | |-- bzip2 | | |-- Makefile (script to execute benchmark, contains commandline used) | | |-- data | | | `-- lgred.source | | `-- mipsver (benchmark binary compiled in ECE511 simulator ISA) | |-- gcc | | |-- Makefile | | |-- data | | | |-- smred.c-iterate.i | | | |-- smred.c-iterate.s | | | |-- tiny.i | | | `-- tiny.s | | |-- mipsver | | |-- small.s | | |-- smred.i | | |-- tiny.1 | | `-- tiny.in | |-- lzw | | |-- Makefile | | `-- mipsver | |-- mcf | | |-- Makefile | | |-- data | | | |-- smred.in | | | `-- test.in | | `-- mipsver | `-- parser | |-- Makefile | |-- data | | |-- 2.1.dict | | |-- smred.in | | |-- super-small.dict | | |-- test.in | | `-- words | | |-- CVS | | | |-- Entries | | | |-- Repository | | | `-- Root | | |-- words.adj.1 | | |-- words.adj.2 | | |-- words.adj.3 | | |-- words.adv.1 ... | | |-- words.v.8.4 | | |-- words.v.8.5 | | `-- words.y | |-- mipsver | `-- words -> data/words |-- arch-listeners.cc |-- arch-listeners.h |-- arch-model (ISA simulator binary) |-- arch-model.cc (The plain ISA simulator) |-- arch-model.h |-- bitops.h |-- btb.h |-- cache.h |-- circuit.cc |-- circuit.h |-- config.h |-- decode.cc |-- decode.h |-- decode_stage.cc |-- decode_stage.h |-- delay.h |-- dependency_window.h |-- elf32.h |-- elf_common.h |-- elf_loader.h |-- endian.c |-- exec_unit.cc |-- exec_unit.h |-- execute.cc |-- execute.h |-- free_list.cc |-- free_list.h |-- frontend_delay_stage.cc |-- frontend_delay_stage.h |-- gcp.h |-- globals.cc |-- globals.h |-- ifetch.cc |-- ifetch.h |-- inorder_scheduler.cc (in-order scheduler) |-- inorder_scheduler.h |-- issue_buffer.h |-- long_vector.h |-- lsq_packets.cc |-- lsq_packets.h |-- lsq_pf.cc |-- lsq_pf.h |-- objdump (used to dis-assemble benchmark binaries) |-- objdump.cc |-- packets.h |-- pipelined-model (pipelined simulator binary) |-- pipelined-model.cc (entry point, main func) |-- polyflow_stats.h |-- pool.h |-- pool_alloc.h |-- pretty_print.cc |-- pretty_print.h |-- reg_data.h |-- regfile_circuit.h |-- rename_stage.cc |-- rename_stage.h |-- rename_stage_common.h (virtual renamer base class) |-- rename_tables.cc |-- rename_tables.h |-- rob.cc |-- rob.h |-- scheduler.cc (Out-of-order scheduler) |-- scheduler.h |-- scheduler_common.h (virtual scheduler base class) |-- sim_endian.h.in |-- sparse_memory.cc |-- sparse_memory.h |-- tag_file.h `-- tags 13 directories, 147 files [vdhar2@localhost ece511-sim]$

The source files for the stages have been highlighted in yellow.

The instructions are passed along from one stage to another in form of a decoder::instr_h object defined in decode.h , which is basically a GCP (garbage collected pointer, gcp.h) wrapper over the instr_rep structure defined in decode.h . Also each instr_h object is uniquely identified by its instr_num field, which is really useful during debugging to identify different instances of the instr from the same PC.

Various other signals like the branch and memory-ordering mispredict etc. are defined in packets.h

The cache is modeled using cache miss time simulation in cache.h

The main memory is modeled using sparse_memory.h

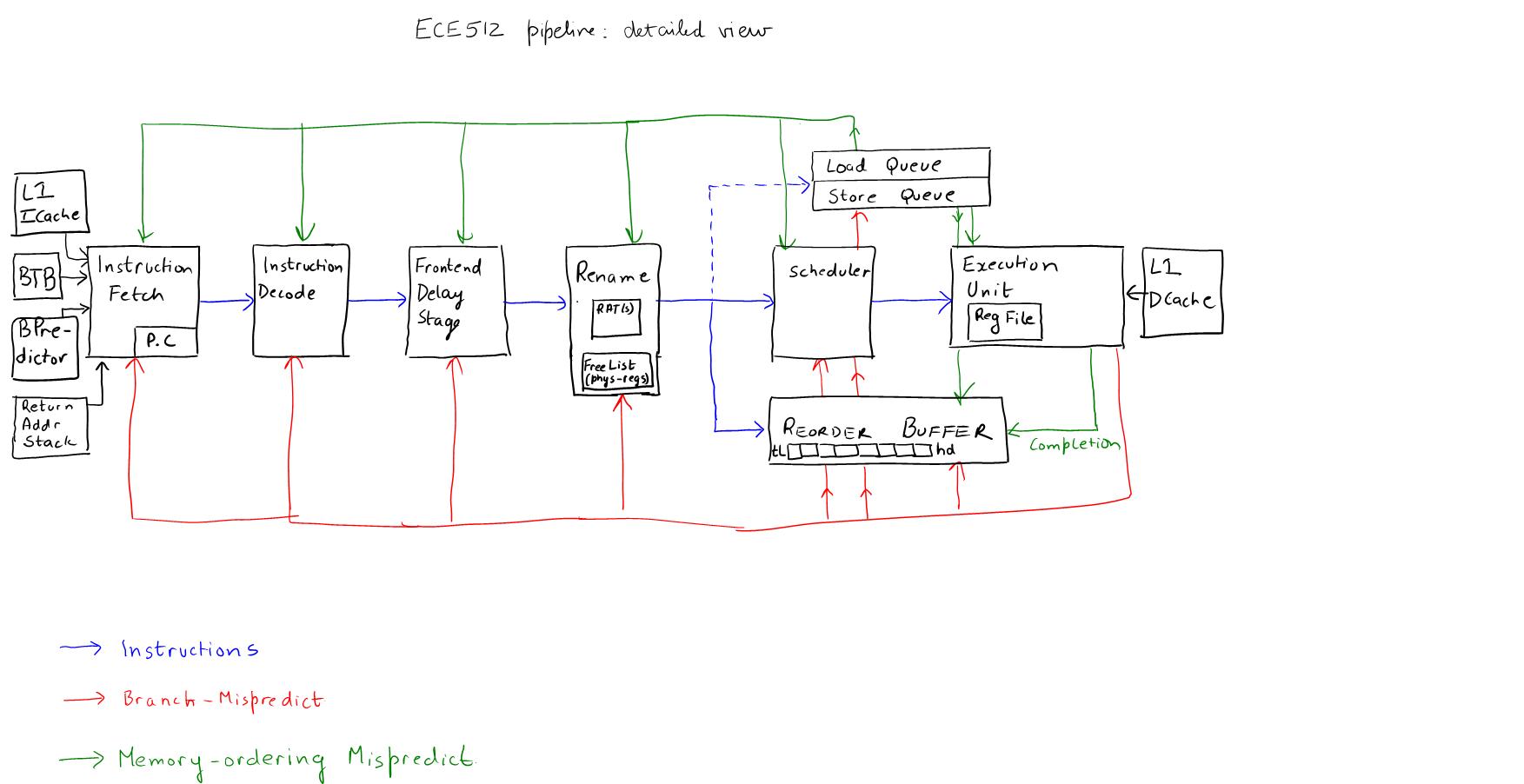

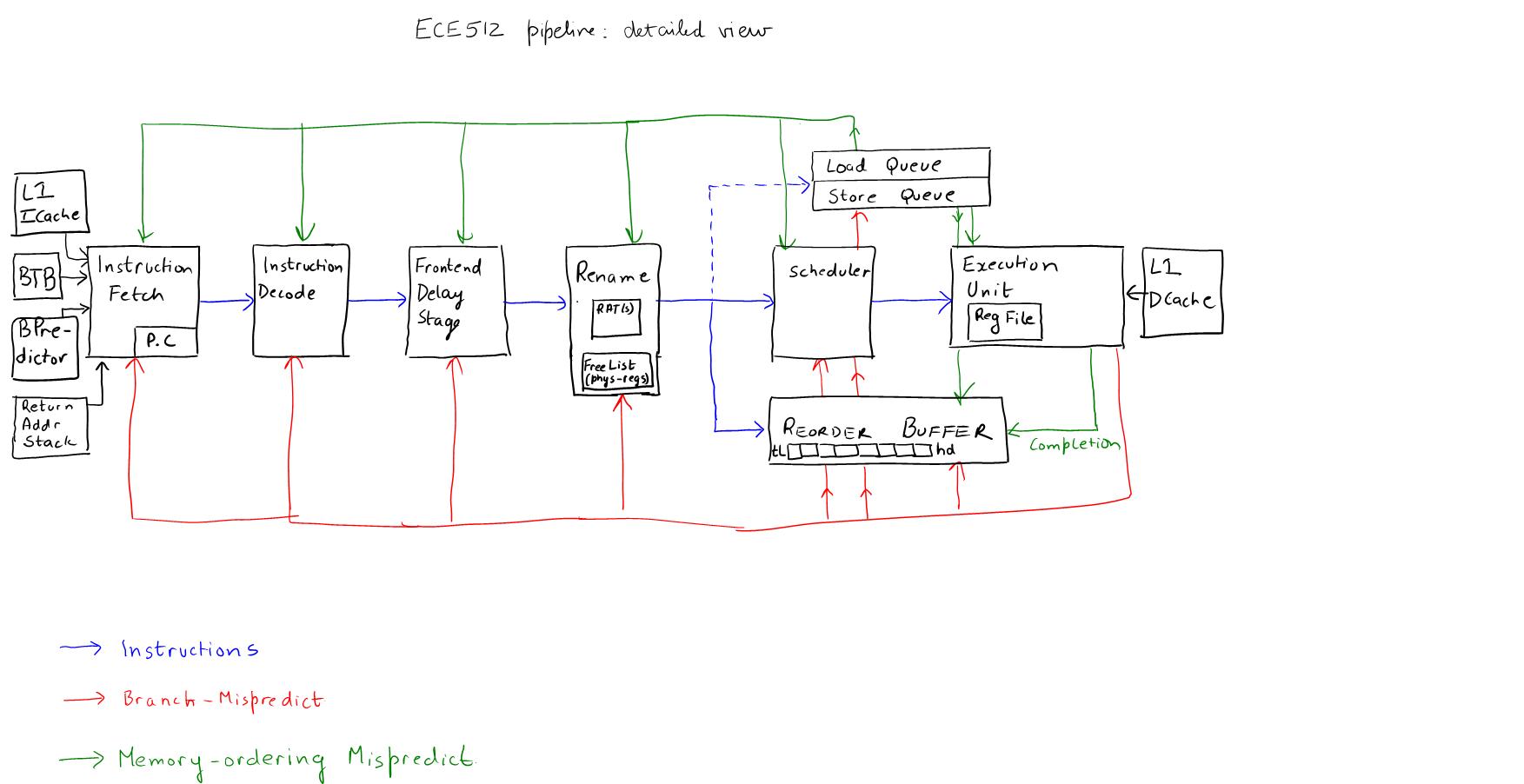

The diagrams used on the ECE512 page are mostly applicable to the simulator and have been replicated below.

NOTE: the ECE511 simulator doesnt have branch prediction (the Bpredictor box above) and renaming (RATs and FL blocks)

Using the -debug command-line flag

../../pipelined-model -debug 0xffff mipsver 800

The flag values for the different stages can be figured out easily in the source code by hunting for the if (debug_mask & 0x001) type statements

Restrict simulation time by using

-stop

-stop_instr

fast forward to a particular cycle, runs the ISA simulator till the specified cycle and then shifts over to pipelined-model

-fast_forward

Using plain old gdb or its wrappers like ddd

Debug source code memory leaks and errors using valgrind

valgrind ?tool=memcheck

Using raw printf() statements. Simple, quick and effective.

In case you are still looking for the ECE512 Spring 2006 helpful hints.

(Last Updated: September 5th )