# LENS CONTROLLER FOR BIOMEDICAL CAMERAS

TA: Zhicong Fan Professor : Viktor Gruev Siddharth Sharma (sharma62) Kevin Sha (ksha3) Jihun Kim (jihunhk2)

#### OVERVIEW

- Introduction & Objective

- Design

- Project Build & Functional Test Results

- Successes & Challenges

- Conclusion & Areas of Improvement

#### INTRODUCTION TO PROJECT

- Margin of error in many medical operations is very slim

- One prime example is cancer treatment :

- It requires high degree of accuracy

- $\circ~$  25% of breast cancer patients, 35% of colon cancer patients, and 40%

- of head and neck cancer patients suffer from incomplete tumor removal

- Hence, this is a significant problem and requires solution.

#### OBJECTIVE

- To remotely control the camera's focus and shutter for use in the operating room

- The desired goal is that the camera's specifications can be adjusted to make sure that the entire tumor(s) is removed

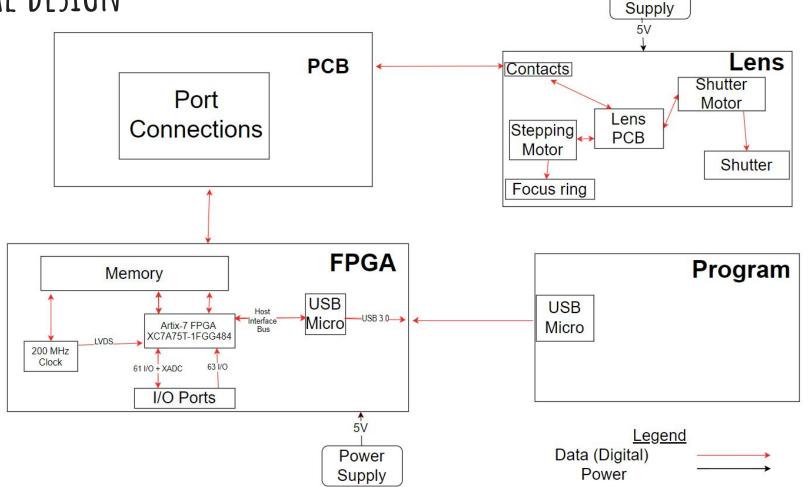

#### ORIGINAL DESIGN

Power

#### CHANGES MADE SINCE THEN: PCB SUB-SECTION

- Redesigned sub-section completely since Design Document

- Originally thought that one flexible PCB would be enough to connect the FPGA and the lens mount

- Found that new system would have to be developed

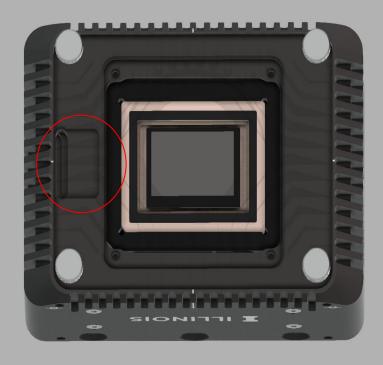

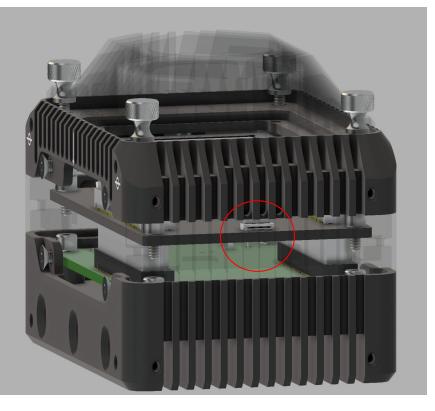

#### PROJECT BUILD: PCB SUB-SECTION

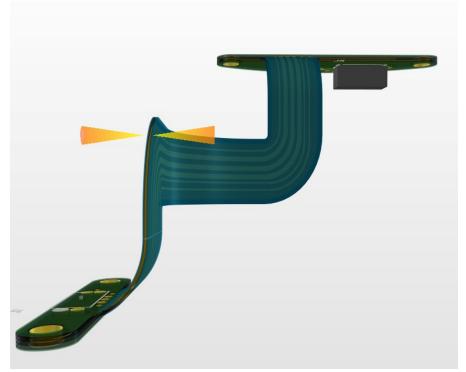

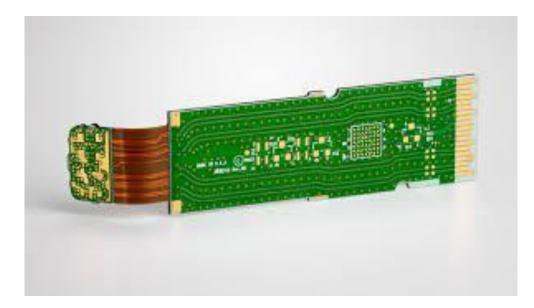

- 2 PCBs:

- $\circ~$  A rigid-flex-rigid which would transport the signals through the

tight constraints of the lens mount

• A flex PCB, which will connect the signals from the FPGA to the the bottom of the lens mount

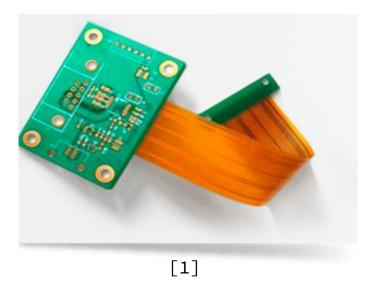

#### RIGID-FLEX PCBS

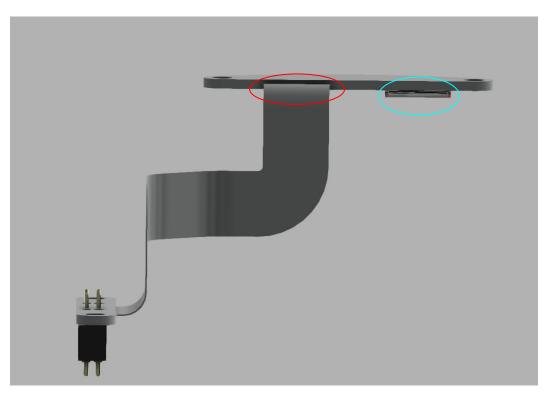

- Rigid section with flex section emerging from the middle

- Allows for rigid PCBs to be placed in tight regions

#### EMERGING FLEX SECTION CONNECTS TWO RIGID SECTIONS

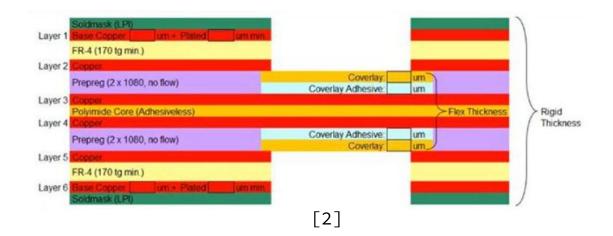

#### LAYER STACKUP

- Important to correctly incorporate layers for optimum signal integrity

- Flex signal layers need to be properly extended

|    | Overlay        |          |    |          |          |    | Overlay        |          |

|----|----------------|----------|----|----------|----------|----|----------------|----------|

|    |                | 1mil     |    |          |          |    | Solder Mask    | 1mil     |

|    | Surface Finish | 0.512mil |    |          |          |    | Surface Finish | 0.512mil |

| L1 | Signal         | 1.378mil |    |          |          | LI | Signal         | 1.378mil |

|    | Adhesive       | 2mil     |    |          |          |    | Adhesive       | 2mil     |

|    | Prepreg        | 7.087mil |    |          |          |    | Prepreg        | 7.087mil |

|    |                |          |    | Coverlay | 0.984mil |    |                |          |

|    |                |          |    | Adhesive | 0.984mil |    |                |          |

| L2 | Plane          | 1.378mil | LI | Plane    | 1.378mil | L2 | Plane          | 1.378mil |

|    | Core           | 8mil     |    | Core     | 8mil     |    | Core           | 8mil     |

| L3 | Signal         | 1.378mil | L2 | Signal   | 1.378mil | L3 | Signal         | 1.378mil |

|    | Prepreg        | 7.087mil |    | Adhesive | 0.984mil |    | Prepreg        | 7.087mil |

|    |                |          |    | Coverlay | 0.984mil |    |                |          |

| L4 | Signal         | 1.378mil |    |          |          | L4 | Signal         | 1.378mil |

|    | Surface Finish | 0.512mil |    |          |          |    | Surface Finish | 0.512mil |

|    | Solder Mask    | 1mil     |    |          |          |    | Solder Mask    | 1mil     |

|    | Overlay        |          |    |          |          |    | Overlay        |          |

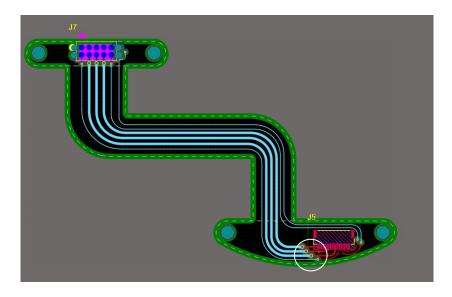

#### ROUTING AND ELECTRICAL CONNECTIONS

- Rigid and flex sections are on different layers

- Signals transported between different layers using vias

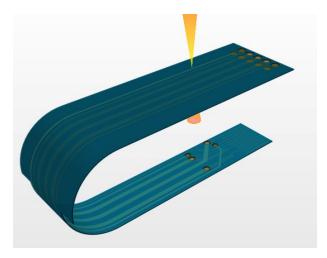

#### BEND ANGLE/BEND RADIUS OF FLEX REGION

• Bend angles are all 90°, experimented with bend

direction

Bend radius was dependent on bend angle

#### FLEX PCBS

• Used to navigate tight mechanical constraints

#### FLEX PCB SPECS

• Flex PCB is used to connect the FPGA connector and the camera body via contact pads and an exposed beveled edge

#### FLEX PCB LAYER STACKUP

|    | Coverlay   | 0.492mil |

|----|------------|----------|

|    | Adhesive   | 0.591mil |

| L1 | Signal     | 0.472mil |

|    | Dielectric | 0.984mil |

| L2 | Signal     | 0.472mil |

|    | Adhesive   | 0.591mil |

|    | Coverlay   | 0.492mil |

#### ROUTING AND WIRE CONNECTIONS

• Beveled edge and contact pads are on the same layer

### SUCCESSES AND FAILURES: PCB SUB-SECTION

#### <u>Successes</u>

- Un-bending the CAD model & making it our board shape

- Using vias to ensure optimal signal routing

- Implementing different layer stackups

- Application of rigid-flex and flex PCB knowledge

#### <u>Failures</u>

- Biggest setback was that we believed that the port mapping of the FPGA connector was the port mapping of the lens connector

- Did not anticipate the process of actually ordering the PCB

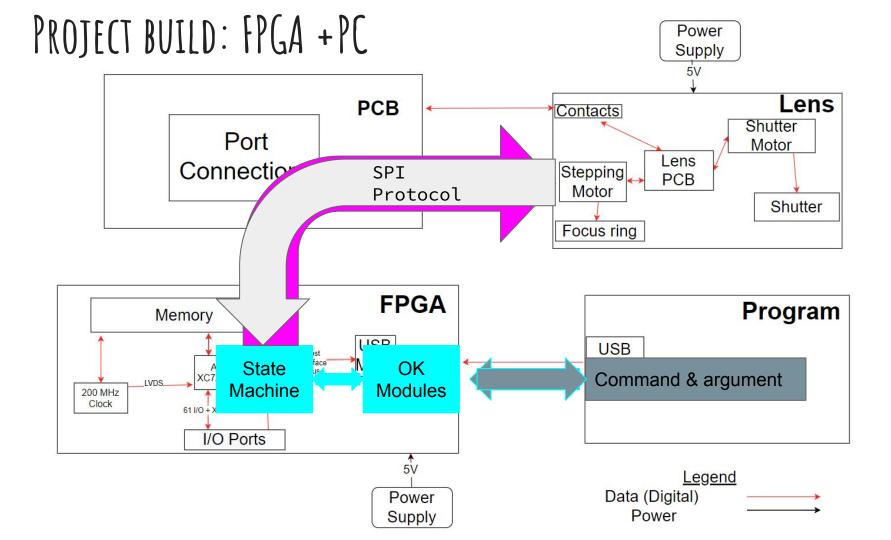

### PROJECT BUILD: FPGA +PC

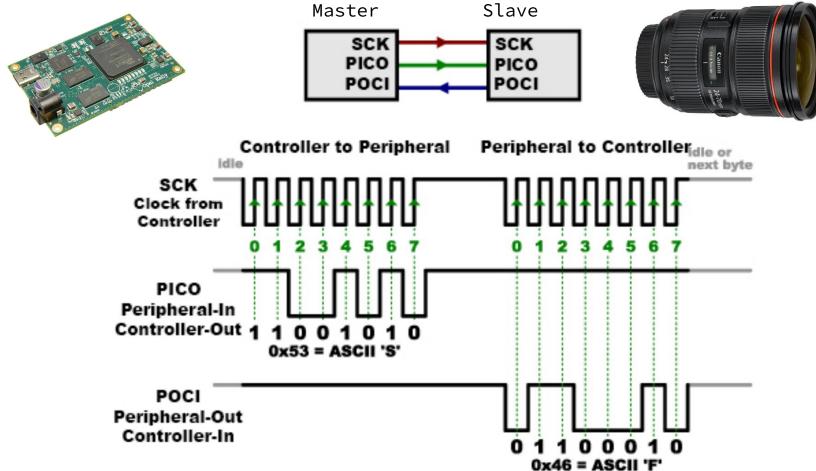

#### <u>FPGA</u>

• XEM7310-A75 (testing purpose)

• XEM7310-A200(in actual design).

- FPGA is for communication between the computer and the lens.

- Lens SPI protocol

- Computer/PC OK modules & python codes

#### <u>PC</u>

• Users will be sending the commands for the lens to the FPGA using the <u>python</u> code on their PC.

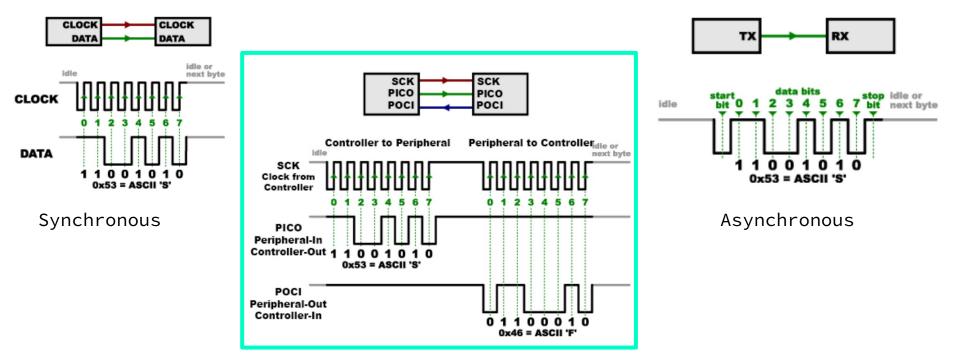

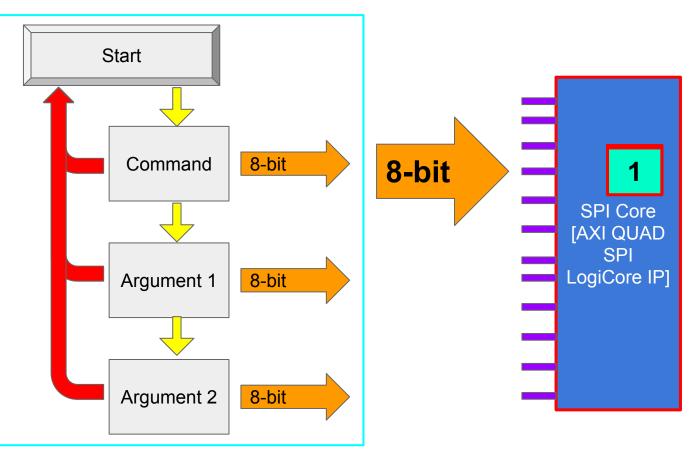

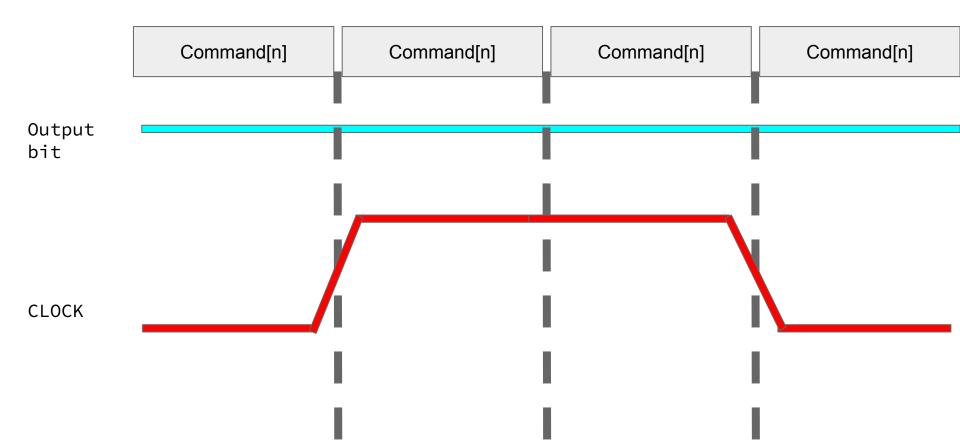

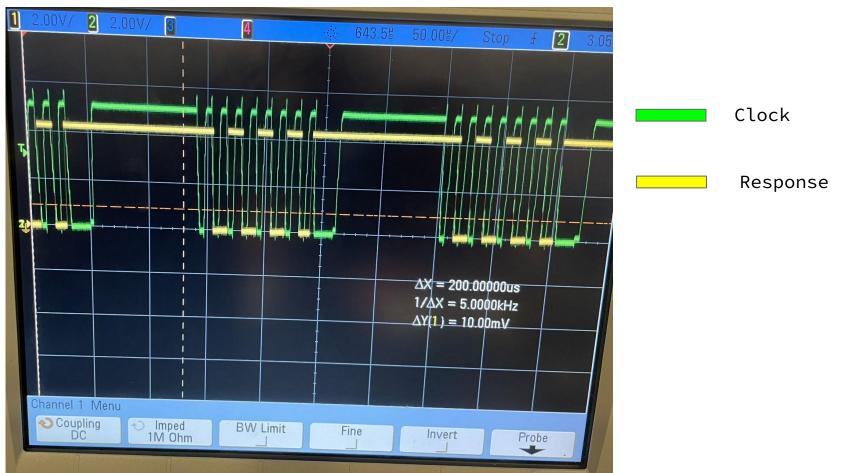

### SERIAL PERIPHERAL INTERFACE (SPI) PROTOCOL

- It is a common interface used to send data between a microcontroller and small peripheral devices such as sensors.

- It consists of clock, data lines, and select line.

#### SPI PROTOCOL

#### PROJECT BUILD: FPGA +PC

- <u>Commands</u>

- **0x12** : Change aperture

- + one 8-bit argument

- Ox44 : Change focus

+ two 8-bit arguments

- $\circ$  **0x05** : Focus to max

• **0x06** : Focus to min

• **OxOA** : Read/sync

### PROJECT BUILD: FPGA +PC

- <u>Python</u>

- $\circ$  Spyder IDE

- Enables us to make PC communicate FPGA.

- <u>Verilog</u>

- $\circ~$  Modules to transfer data between FPGA and PC.

- OkWireIn

- OkWireOut

- State Machine

- Transfer and receive data in between the FPGA and the lens using SPI protocol

#### PYTHON

| 68<br>69<br>70<br>71<br>72                                                                   | <pre>variable_1 = 10 # command<br/>variable_2 = 14 # argument1<br/>variable_3 = 0 # argument2<br/>variable_4 = 0</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 73<br>74<br>75<br>76<br>77<br>78                                                             | <pre>print("Variable 1 is initilized to " + str(int(variable_1))) print("Variable 2 is initilized to " + str(int(variable_2))) print("Variable 3 is initilized to " + str(int(variable_3))) print("Variable 3 is initilized to " + str(int(variable_4)))</pre>                                                                                                                                                                                                                                                                                                                     |

| 79<br>80<br>81<br>82<br>83<br>84<br>85<br>86<br>85<br>86<br>87<br>88<br>90<br>91<br>92<br>93 | <pre>dev.SetWireInValue(0x00, variable_1) #Input: data for Variable 1 using mamoery spate<br/>dev.SetWireInValue(0x01, variable_2) #Input: data for Variable 2 using mamoery spate<br/>dev.SetWireInValue(0x02, variable_3)<br/>dev.SetWireInValue(0x03, variable_4)<br/>dev.UpdateWireIns() # Update the WireIns<br/>while variable_4 == 0:<br/>dev.UpdateWireOutValue(0x21)<br/>response = dev.GetWireOutValue(0x20)<br/>print("response is : " + str(int(response)))<br/>if RET == 1:<br/>variable_4 = 1<br/>dev.SetWireInValue(0x03, variable_4)<br/>dev.UpdateWireIns()</pre> |

| 94<br>95<br>96<br>97<br>98                                                                   | <pre>variable_1 = 10 # command<br/>variable_2 = 14 # argument1<br/>variable_3 = 0 # argument2<br/>variable_4 = 0</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 99<br>100<br>101<br>102<br>103                                                               | <pre>print("Variable 1 is initilized to " + str(int(variable_1))) print("Variable 2 is initilized to " + str(int(variable_2))) print("Variable 3 is initilized to " + str(int(variable_3))) print("Variable 3 is initilized to " + str(int(variable_4)))</pre>                                                                                                                                                                                                                                                                                                                     |

| 102<br>104<br>105<br>106<br>107                                                              | <pre>dev.SetWireInValue(0x00, variable_1) #Input data for Variable 1 using mamoery span<br/>dev.SetWireInValue(0x01, variable_2) #Input data for Variable 2 using mamoery span<br/>dev.SetWireInValue(0x02, variable_3)<br/>dev.SetWireInValue(0x03, variable_4)</pre>                                                                                                                                                                                                                                                                                                             |

#### VERILOG

okWireIn wire10 ( .okHE(okHE), .ep addr (8'h00) okWireOut wire20 ( .okHE(okHE), .ep dataout (variable 1)); .okEH(okEHx[ 0\*65 +: 65 ]), .ep addr (8'h20) okWireIn wire11 ( .okHE (okHE), .ep addr (8'h01) .ep datain( {24'b0, response} ) .ep dataout(variable 2)); ); okWireIn wire12 ( .okHE (okHE), okWireOut wire21 ( .okHE(okHE), .ep addr(8'h02) .okEH(okEHx[ 1\*65 +: 65 ]), .ep dataout (variable 3)); .ep addr(8'h21), okWireIn wire13 ( .okHE (okHE), .ep datain( {31'b0, FIN} )); .ep addr (8'h03)

.ep\_dataout(variable\_4));

RET = dev.GetWireOutValue(0x21) response = dev.GetWireOutValue(0x20)

dev.SetWireInValue(0x00, variable\_1)

dev.SetWireInValue(0x01, variable\_2)

dev.SetWireInValue(0x02, variable\_3)

dev.SetWireInValue(0x03, variable\_4)

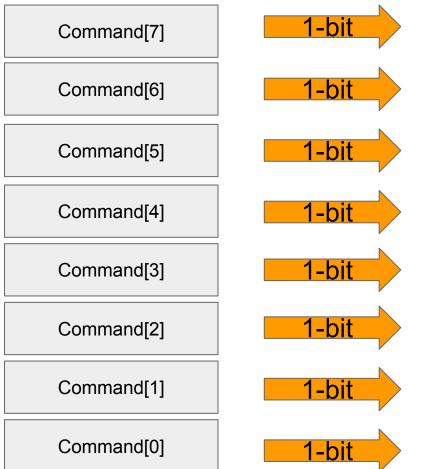

### VERILOG (STATE MACHINE) - INITIAL VERSION

#### VERILOG (STATE MACHINE) - SECOND VERSION

#### VERILOG (STATE MACHINE) - SECOND VERSION

Command[7]

Command[6]

Command[5]

Command[4]

Command[3]

Command[2]

Command[1]

Command[0]

#### VERILOG (STATE MACHINE) - SECOND VERSION

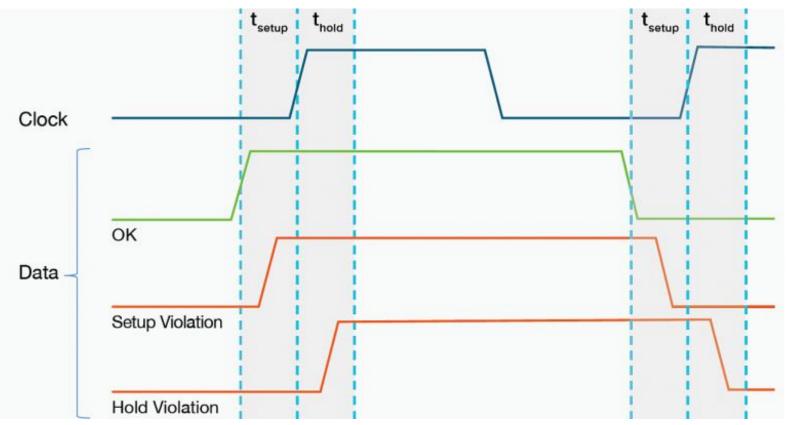

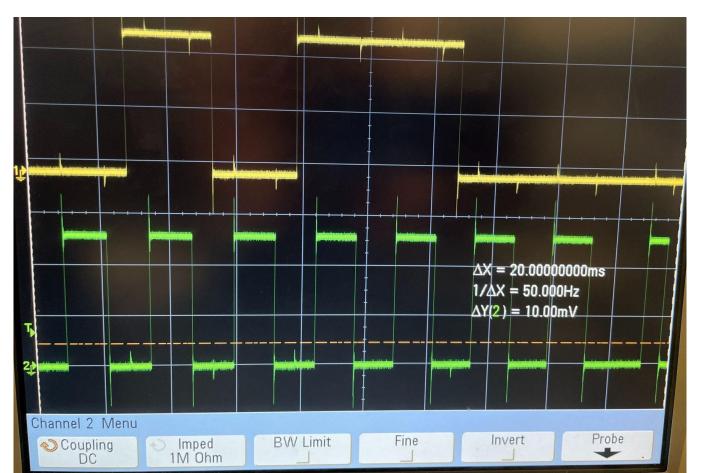

### VERILOG (STATE MACHINE) - THIRD VERSION

• <u>Setup and Hold Time Violation</u>

#### VERILOG (STATE MACHINE) - THIRD VERSION

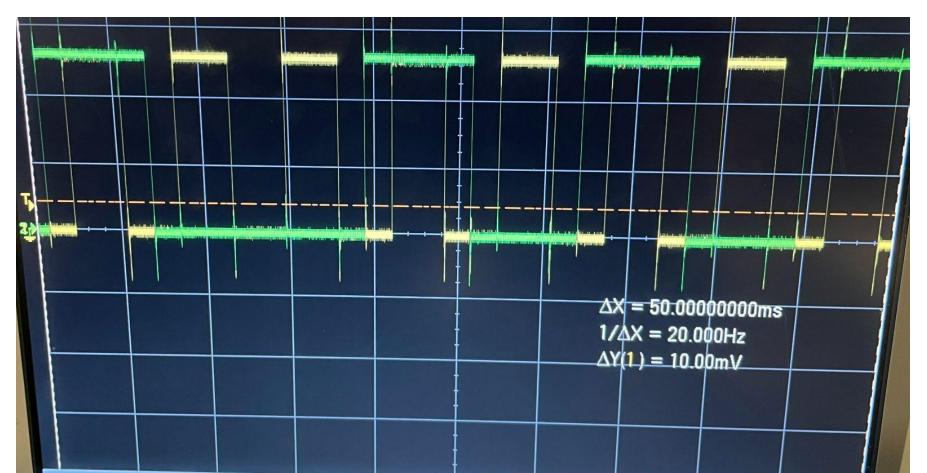

#### SUCCESSES AND FAILURES: FPGA SUB-SECTION

#### SUCCESSES AND FAILURES: FPGA SUB-SECTION

#### SUCCESSES AND FAILURES: FPGA SUB-SECTION

### SUCCESSES AND FAILURES: FPGA + PC

#### <u>Successes</u>

- Managed to get the lens to move according to the command input by the user

- Managed to carry out SPI protocol using the state machine through the verilog code without using standard IP block

#### <u>Failures</u>

• There are certain values that we need to put in for the argument. We did not have enough time to figure out what are the available argument values.

### WHAT DID WE LEARN? (TECHNICAL)

- SPI Protocol

- General Process of engineering

- Implementation/Code => Simulation => Testing => Debugging => Success

- OK Modules

- Rigid-Flex/Flex PCBs

- Layer stackup requirements

- Routing rules

- Routing debugging

- Navigating mechanical design constraints

- Vias and Tented Vias

### WHAT DID WE LEARN? (SOFT SKILLS)

- Ask more questions to prevent misunderstandings later

- Being seen as 'dumb' for asking certain questions

- Always have a time cushion for every step

- Dealing with setbacks and how to move forward from them

#### CONCLUSION AND FINAL THOUGHTS

- Proud of what we have accomplished, disappointed we couldn't make it a reality

- Learned hard lessons to carry with us into the future

- Enjoyed putting our skills to the test and picked up necessary knowledge to achieve our goals

- Picked the right team members to do this project with

#### ETHICAL CONCERNS

- Privacy concerns using the camera

- Mechanical hazards in the event of an accident

## SPECIAL THANKS TO

#### • Illinois BioSensors Lab

- $\circ\,$  Professor Viktor Gruev

- $\circ$  Zhongmin Zhu

- Our TA: Zhicong Fan

#### CITATIONS

[1] "Home," *Flex PCBs* | *Rigid Flex PCBs* | *PCB Unlimited*. [Online]. Available: https://www.pcbunlimited.com/products/rigid-flex-pcbs. [Accessed: 24-Nov-2022].

[2] "What is Flex PCB? - an overview of Flex and Rigid-Flex PCB - news," *PCBway*. [Online]. Available: https://www.pcbway.com/blog/News/What\_is\_Flex\_PCB\_\_\_\_An\_Overview\_of\_Flex\_and\_Rigid\_Flex\_PCB.html. [Accessed: 24-Nov-2022].

[3]"Basics of Flex Circuit Design - Minco Products." [Online]. Available:<u>https://www.minco.com/wp-content/uploads/Minco\_BasicsofFlexDesign.pdf</u> [Accessed: 29-Sep-2022].

[4] M. Grusin, "Serial Peripheral Interface (SPI) - learn.sparkfun.com," *Sparkfun.com*, 2019. <u>https://learn.sparkfun.com/tutorials/serial-peripheral-interface-spi/all</u>

[5] "Final thoughts images – browse 2,487 stock photos, vectors, and video," Adobe Stock. [Online]. Available: https://stock.adobe.com/search?k=final+thoughts. [Accessed: 27-Nov-2022].

[6] "Ethics issues in the engineering profession," Railway Age, 12-Sep-2022. [Online]. Available: https://www.railwayage.com/regulatory/ethics-issues-in-the-engineering-profession/. [Accessed: 27-Nov-2022].