### Post-break recall

### Recap + reminders

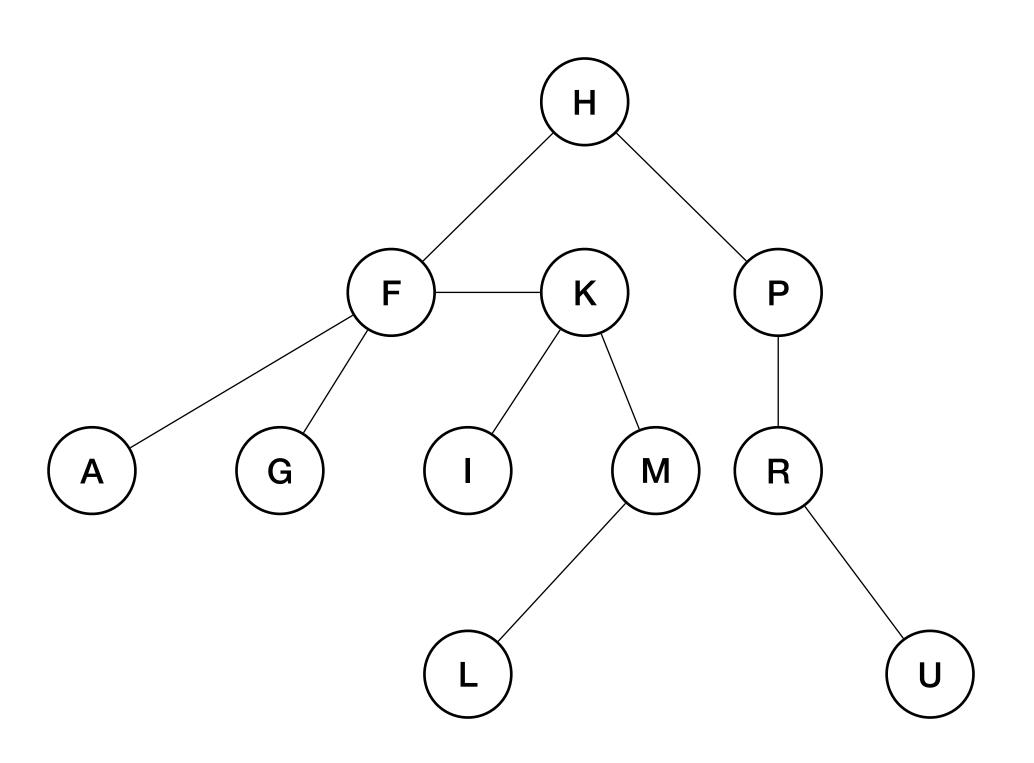

- Trees

- Concepts & properties

- Traversals: preorder/ inorder/postorder

- Binary search trees

- C to LC3 (structs, trees, linked lists)

- Code posted

- Reminders

- Extra credit quiz

- Programming competition

- ICES forms available

## Today

- Change gears & talk about interrupts in LC3

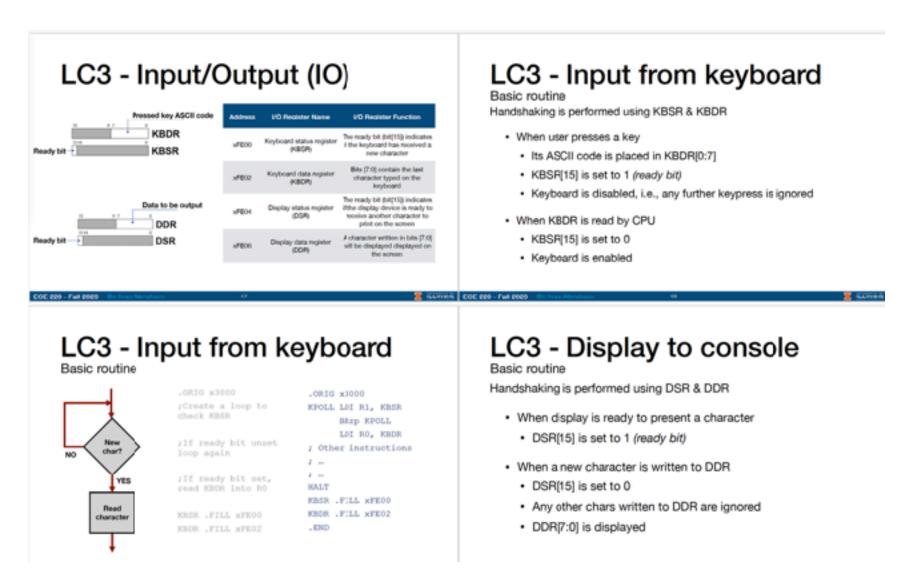

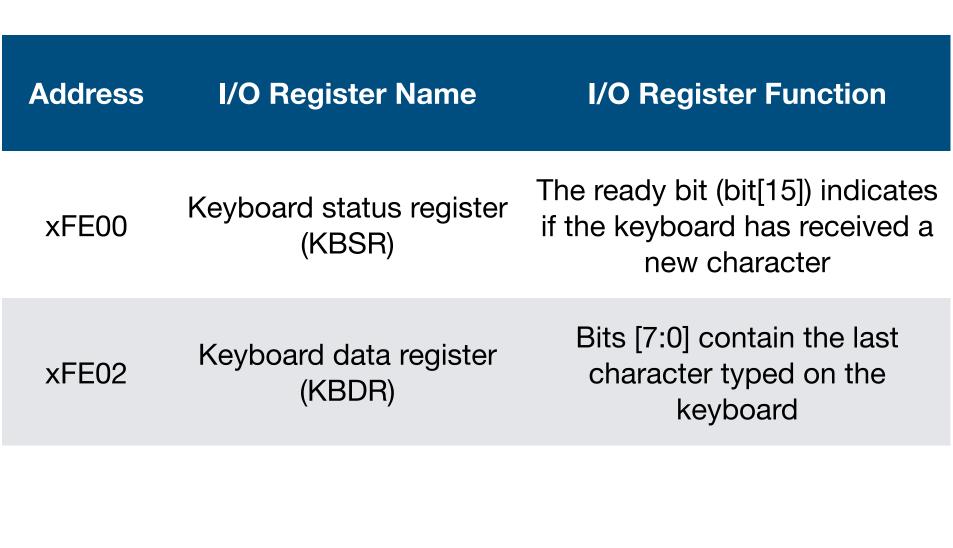

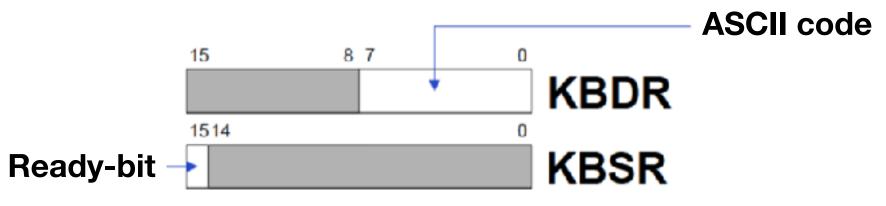

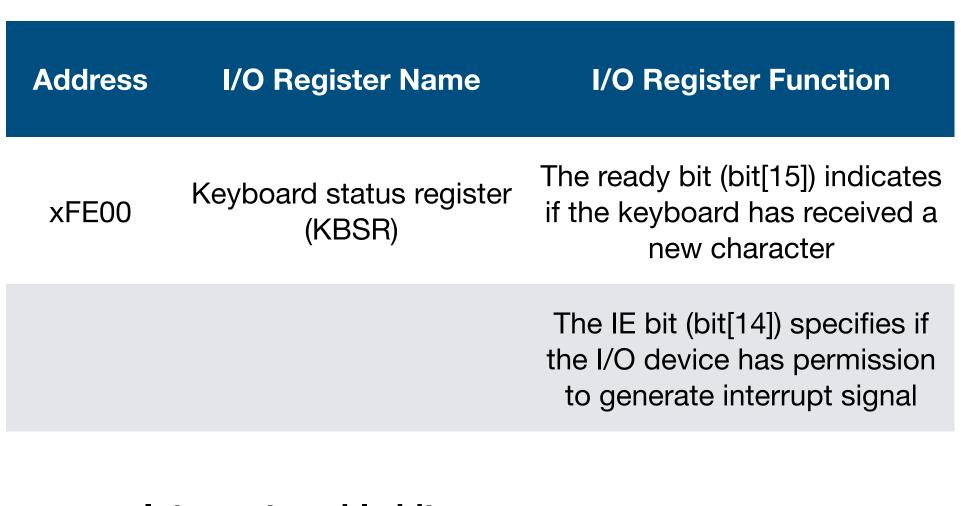

- Recall: KBSR/KBDR & DSR/DDR?

- When did we see these acronyms?

- How did we implement I/O in LC3 before?

**Slides from Lecture #1**

### Previously - I/O using Polling or TRAPs

Figure A.1 - P&P 3rd Ed.

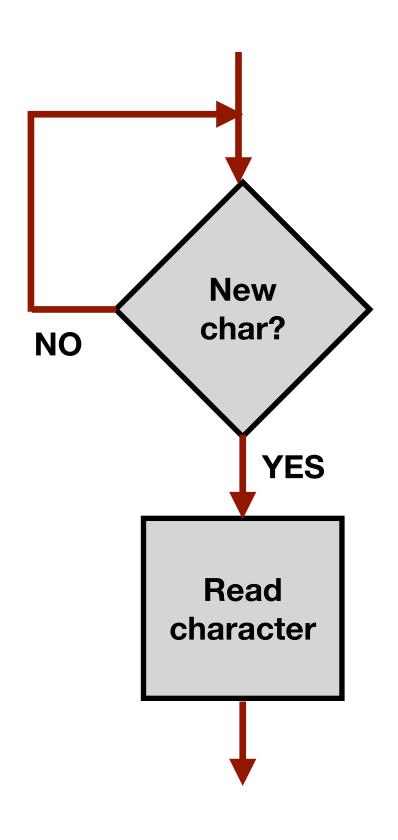

### Any problems with polled I/O?

- Suppose we want to type 100 characters:

- User can input at speed of 60 WPM, assume, eight characters/word:

- How long to type 100 characters?

- Processor cannot do anything else while it waits on next character!

- 12.5 seconds spend just polling!

- How can we free up the processor to do other tasks?

### Interrupt driven I/O

- Key idea: An I/O device can

- force running program to stop

- have processor execute different program that carries out needs of I/O device, and then

- resume execution of stopped program as if nothing had happened

```

Program A is executing instruction n

Program A is executing instruction n+1

Program A is executing instruction n+2

1: Interrupt signal is detected

1: Program A is put into suspended animation

1: PC is loaded with the starting address of Program B

2: Program B starts satisying I/O device's needs

2: Program B continues satisfying I/O device's needs

2: Program B continues satisfying I/O device's needs

2: Program B finishes satisfying I/O device's needs

3: Program A is brought back to life

Program A is executing instruction n+3

Program A is executing instruction n+4

```

Figure 9.17 Instruction execution flow for interrupt-driven I/O.

# Now - I/O using interrupts

Figure A.1 - P&P 3rd Ed.

### What needs to happen?

For interrupt driven I/O to work:

- 1. The I/O device must want service.

- Ready bit

- 2. The device must have the **right to request** the service.

- Interrupt enable bit

- 3. The device request must be **more urgent** than what the processor is currently doing.

- Priority levels: PL0 PL1 < ... < PL6</li>

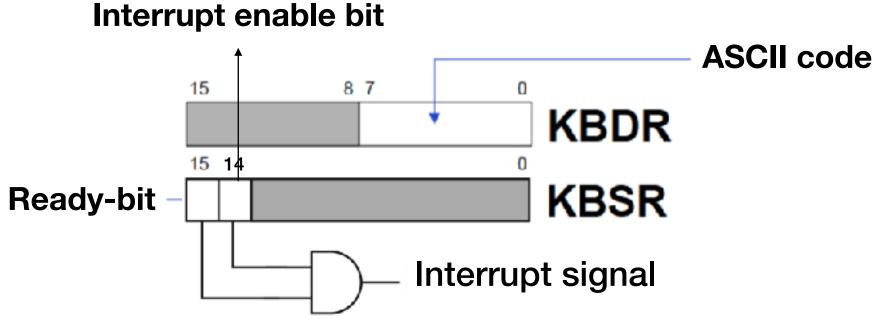

# Generating an INTerrupt

- All devices asserting an interrupt signal are compared

- Highest PL request is compared to current program's PL

- Interrupt is initiated.

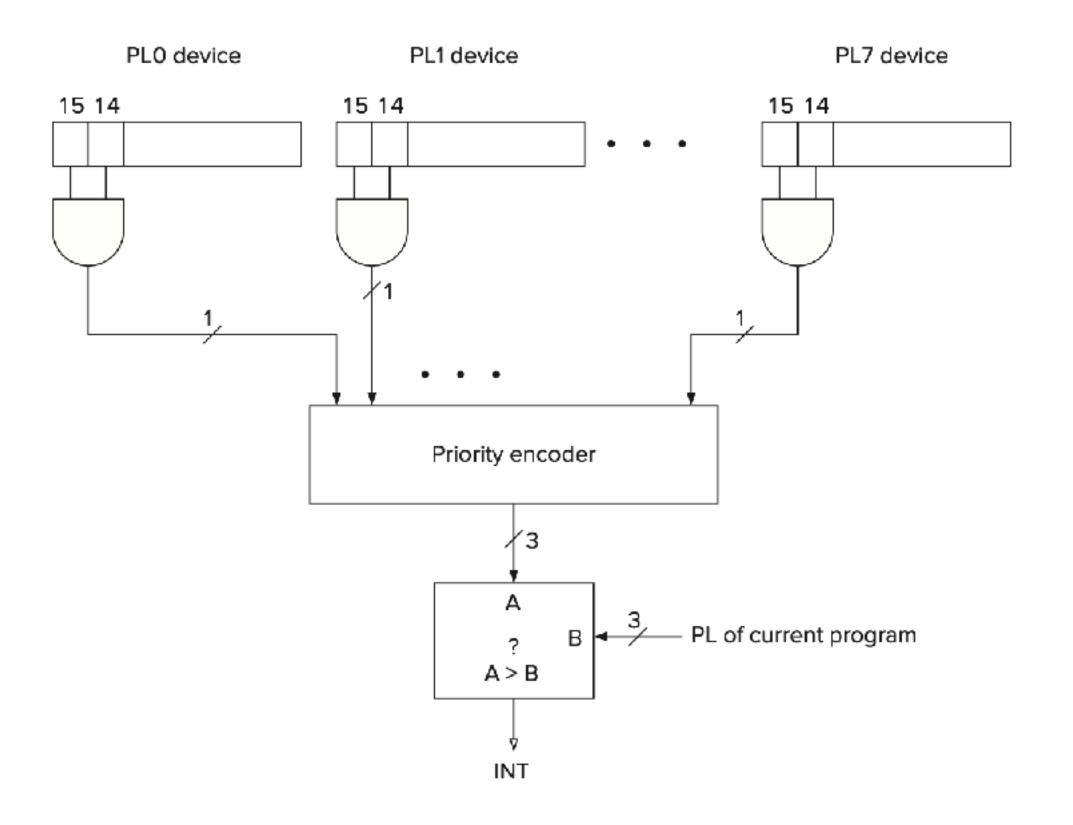

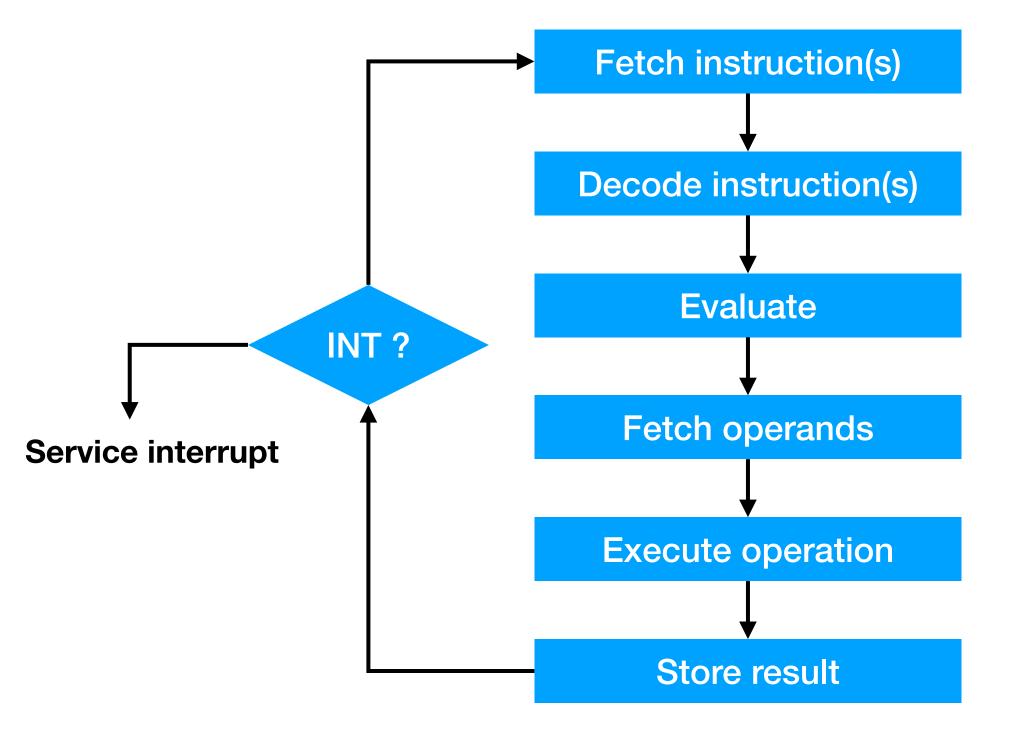

### How processor detects INTerrupts

- Recall instruction cycle.

- Processor will check if INT is asserted at the end of each instruction cycle before starting a new FETCH

### How processor detects INTerrupts

- Control unit needs to:

- save state information to be able to resume interrupted program

- load PC with the starting address of ISR (interrupt service routine)

- resume old process on RTI (coming later)

# Handling the INTerrupt

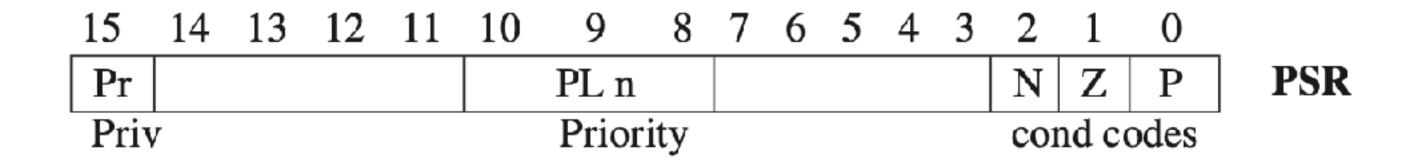

- What should be saved for program to resume?

- PC (Program Counter)

- Processor Status Register (PSR)

- What about GPRs?

- Callee saved

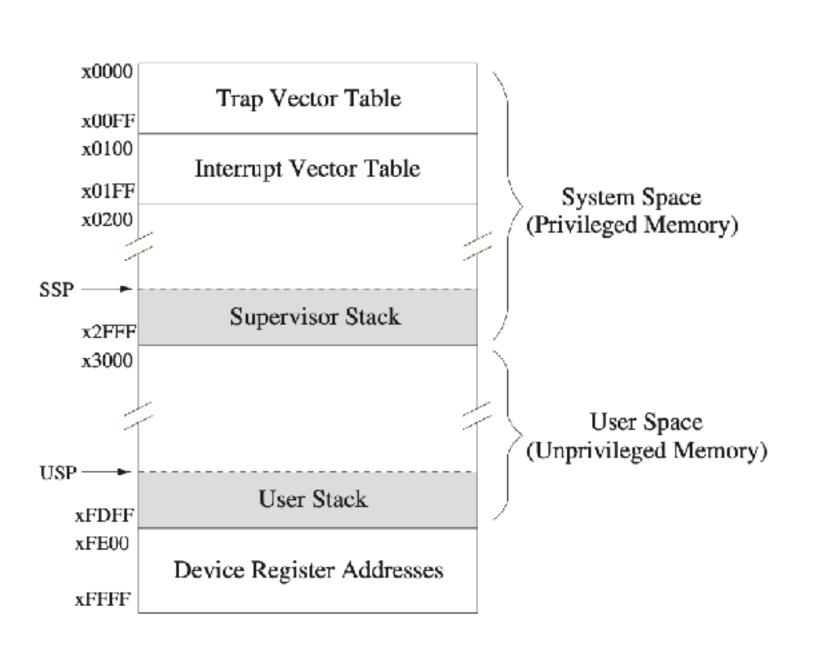

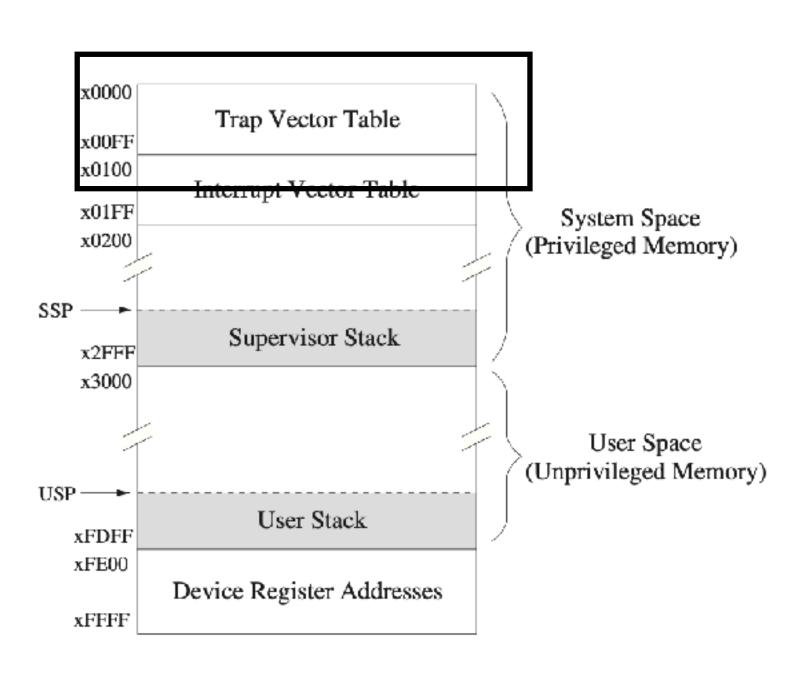

# Privilege vs. priority

### Privilege

• Privilege is all about the right to do something, such as execute a particular instruction or access a particular memory location.

### Priority

Priority is all about the urgency of a program to execute. Every program is assigned a priority, specifying its urgency as compared to all other programs.

See Section 9.1.1.3

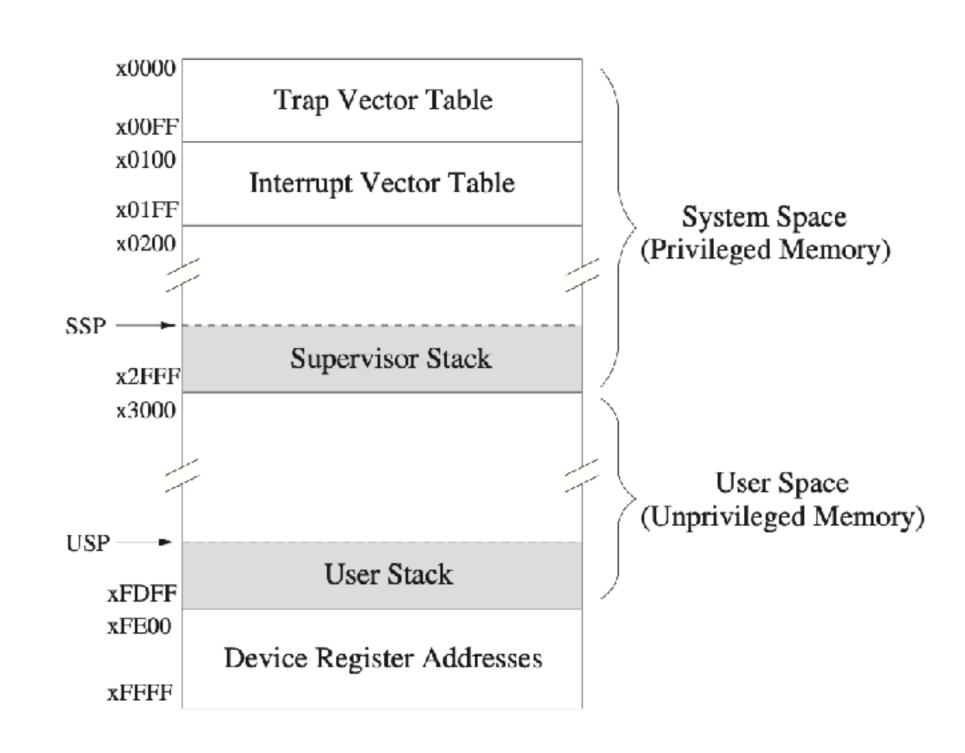

### User stack vs. supervisor stack

- Portion of privileged memory reserved for stack in supervisor mode (why?)

- R6 is used to denote active TOS always.

- Can only run in user or supervisor mode at a time.

- Save R6 on switching modes using (built-in) registers, Saved\_SSP and Saved\_USP

Figure A.1 - P&P 3rd Ed.

## Handling the INTerrupt

- The I/O device generating the INT signal also provides an 8-bit interrupt vector INTV which identifies the device

- INTV will determine which ISR to be executed to service the interrupt

- Similar to TRAP vector table we have seen previously

## Summary of steps

- 1. Processor detects asserted INT along with INTV

- 2. Save R6 to Saved USP. Set R6 to Saved SSP.

- 3. Push PSR & PC to supervisor stack

- 4. Set PSR[15]=0 and set PSR[10:8] = priority of ISR

- 1. Set PSR[2:0]=010 (arbitrarily sets condition codes) —— 3rd Ed.

- 5. Load MAR with x01vv, where vv = 8-bit interrupt vector, then load MDR

- 6. Set PC=MDR

See Section 9.4.5.1

### Returning from (TRAP or) INTerrupt: RTI

- Both TRAP routines and INTerrupt routines end with the RTI instruction.

- Pop PC & PSR from supervisor stack

- If PSR[15]=1,

R6=Saved.USP

- RTI is privileged

### **RTI**

Return from Trap or Interrupt

#### Assembler Format

```

RTI Encoding

15 12 11 0

1000 00000000000

```

### Operation

```

if (PSR[15] == 1)

Initiate a privilege mode exception;

else

PC = mem[R6]; R6 is the SSP, PC is restored

R6 = R6+1;

TEMP = mem[R6];

R6 = R6+1; system stack completes POP before saved PSR is restored

PSR = TEMP; PSR is restored

if (PSR[15] == 1)

Saved_SSP=R6 and R6=Saved_USP;

```

#### Description

If the processor is running in User mode, a privilege mode exception occurs. If in Supervisor mode, the top two elements on the system stack are popped and loaded into PC, PSR. After PSR is restored, if the processor is running in User mode, the SSP is saved in Saved\_SSP, and R6 is loaded with Saved\_USP.

#### Example

RTI ; PC, PSR  $\leftarrow$  top two values popped off stack.

## Interrupt example

```

x3000

.ORIG

What does this

LEA

RO, ISR KB

STI

RO, KBINTV; load ISR address to INTV

program do?

LD

R3, EN IE

STI

R3, KBSR

; set IE bit of KBSR

LD

RO, NUM2

AGAIN

OUT

BRnzp

AGAIN

ST

R0, SaveR0; callee-save R0

ISR KB

LDI

RO, KBDR

; read a char from KB and clear ready bit

OUT

LD

R0, SaveR0; callee-restore R0

HALT

.FILL

x4000; To enable the IE bit

EN IE

NUM2

.FILL

x0032; ASCII Code for '2'

Interrupt

KBSR

.FILL

xFE00

KBDR

•FILL

xFE02

KBINTV

•FILL

x0180; INT vector table address for keyboard

SaveR0

.BLKW

#1

.END

```

### Exceptions

- Exceptions happen when something ... well unexpected happens within the processor.

- Examples: Privilege mode violation (PMV), illegal/invalid opcodes, accessing privileged memory (ACV)

- Exception services routines occupy memory locations x0100 to x017F, mechanism exactly like INTerrupts except ...

- Priority level is not changed.

# Next lecture(s)

- Examples

- Course review: <a href="https://surveys.illinois.edu/sec/1742038613">https://surveys.illinois.edu/sec/1742038613</a>

- So far only C++ and recursion

- Exam preparation tips

- ICES forms