000000000 01010100 30011100 00002020 20202E4F 52494720 20207833 3030300A E0001300 20204C45 41202052 1C3015C0 794C696E 6509E200 13000000 20202020 4C454120 2052312C 206D794C 696E6540 4F502020 60001600 00004C4F 52205230 2C205231 2C202330 21F00010 00000020 20202020 20202054 52415020 78323105 24001400 00002020 20204C44 20204C44 20205232 2C207465 726D8014 00160000 00202020 20202020 20414444 2052322C 20523002 20202020 00002020 20202020 20204252 7A201854 (F506 12 00 5) 00 02 00120000 00202020 20202020 20421244 (F506 12 00 5) 00 02 2020 20202020 20414444 2052312C 2052312C 04001000 20204841 4C54D0FF 2031F90F 4C4C2020 20784646 44306900 00010000 00746572 6D202020 202E4649 00697400 Lecture x0000 - 08/27 00324000 00010000 00010000 00627200 00010000 00010000 00010000 002D6500 00010000 00666100 00010000 00613200 0001000000810008 00010000 00653200 00010000 00323200 00010000 00323000 00010000 002A0000 00636500 00300000 00010000 202E5354 52494E47 5A202020 20226974 61627261 68324066 6132332D 32302200

Slides based on material by: Yuting Chen, Yih-Chun Hu & Ujjal Bhowmik

ECE 220 - Fall '24

**Dr. Ivan Abraham**

# **Course logistics**

- Lectures: Tuesdays & Thursday  $\bullet$

- Three sections offered by different instructors

- Prof. Yuting Chen (1230, BL1), Prof. Yih-Chun Hu (1100, BL2) and this one (1400, BL3).

- Labs: Fridays ullet

- Starts on the hour, every hour from 0900 hrs until 1650 hrs

- Office hours: Schedule posted to <u>website</u>  $\bullet$

# Course logistics

- <u>Course Website</u> (and syllabus)

- Grading: Gradescope + autograder

- Discussions: Campuswire

- Quizzes: CBTF

- Machine problems (MPs): Github

- Textbook: Patt & Patel (3rd Ed)

# Course logistics

- MPs: 12 in total, lowest dropped (except MP 12)

- Quizzes (in-person in CBTF): 6 total, lowest dropped

- Exams (in-person, on-paper): 09/26 and 10/31

- Labs: make up points lost on MPs

| Group            | Weight |

|------------------|--------|

| Labs             | 0%     |

| Machine Problems | 15%    |

| Midterms         | 40%    |

| Final Exam       | 25%    |

| Quizzes          | 20%    |

| Total            | 100%   |

# Syllabus

ECE 220 - Fall '24Dr. Ivan Abraham

# Quick recap of ECE 120

ECE 220 - Fall '24Dr. Ivan Abraham

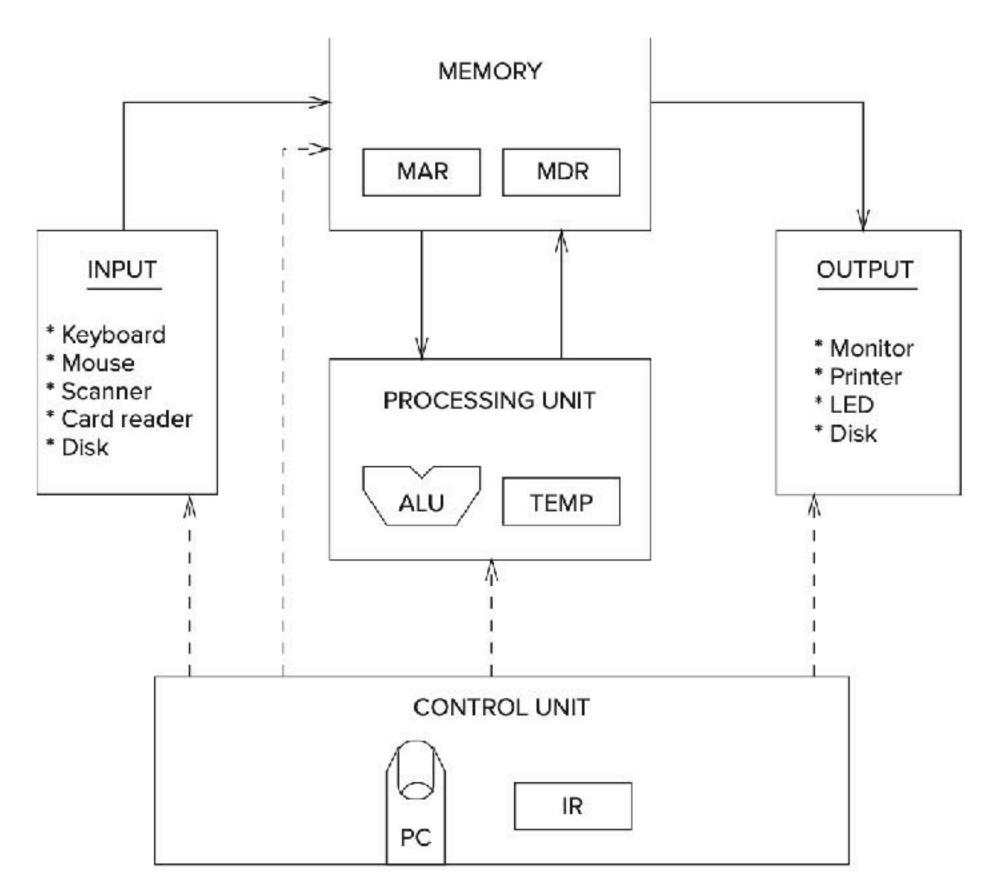

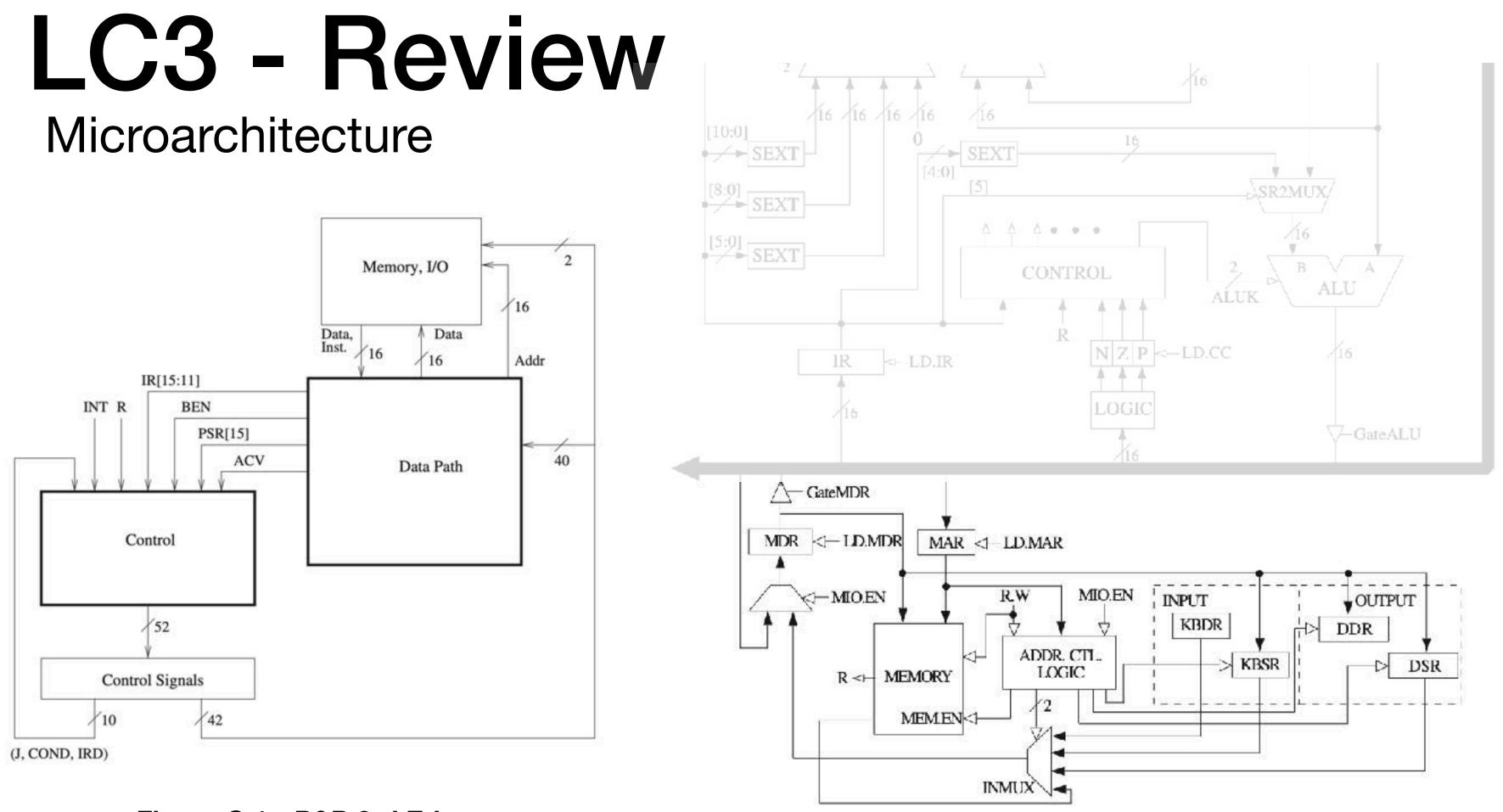

## **Computation** Von Neumann model

- Five major components:

- 1. Memory

- 2. Input

- 3. Output

- 4. Processing unit

- 5. Control unit

### Figure 4.1 - P&P 3rd Ed.

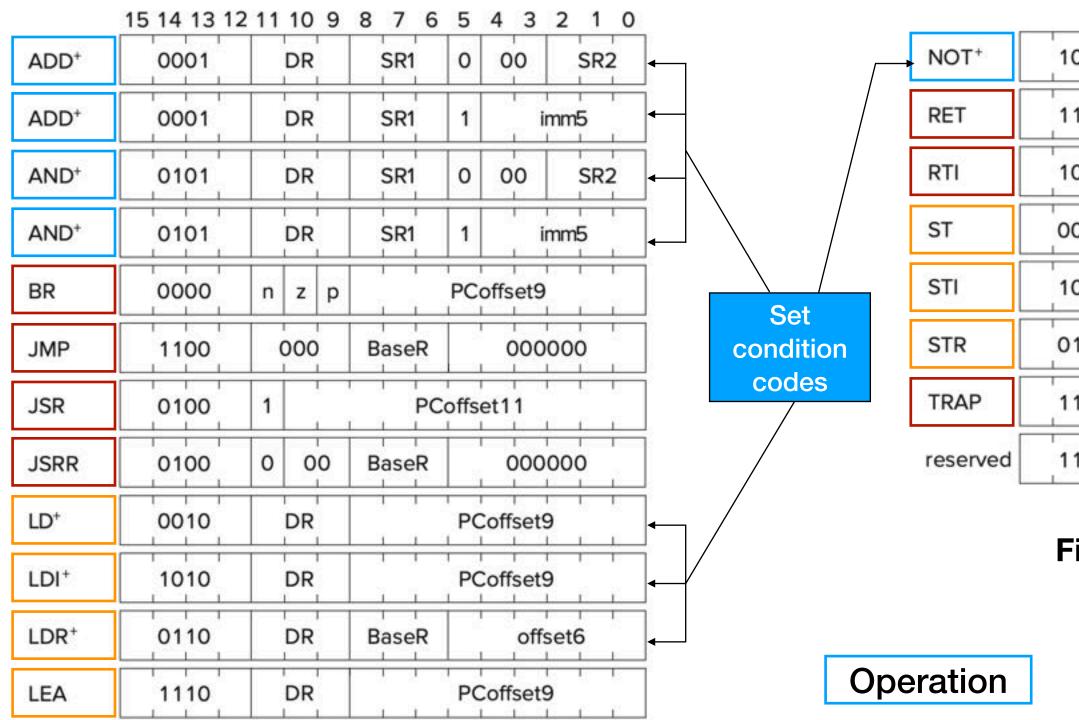

## LC3 Review

- Eight GPRs denoted R0, R1, ..., R7

- Data type: 16-bit 2's complement integers

- Addressing: Locations x0000 xFFFF contain 16 bits each

- Addressing modes:

- Immediate, register, PC-relative, base + offset, indirect

## LC3 - Review Instruction set

Data movement

### Program flow

### Figure A.2 - P&P 3rd Ed.

| NA  | - 15A |         |                   |

|-----|-------|---------|-------------------|

| 001 | DR    | SR      | 111111            |

| 100 | 000   | 111     | 000000            |

| 000 |       | 000000  | 000000            |

| 011 | SR    |         | Coffset9          |

|     |       |         |                   |

| 011 | SR    | P       | Coffset9          |

| 111 | SR    | BaseR   | offset6           |

| 111 | 0000  |         | trapvect8         |

| 101 |       |         |                   |

|     |       | 7 a a 3 | The second second |

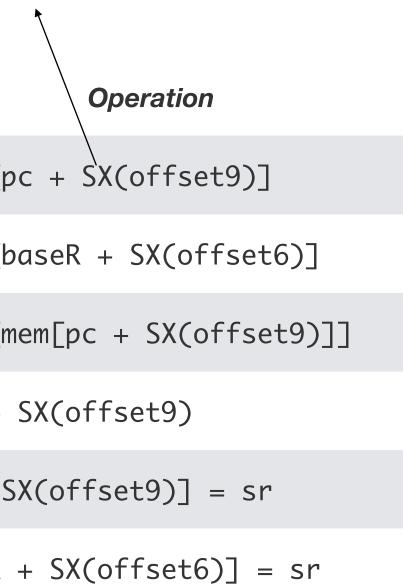

## LC3 - Review Addressing modes

- PC relative, the address is calculated by adding an offset to the incremented program counter, PC.

- **Register relative**, address is read from a register.  $\bullet$

- Indirect, address is read from a memory location who's address is calculated by adding an offset to the incremented program counter.

- Load effective address (LEA), address is calculated by adding an offset to the incremented program counter. The address itself (not its value) is stored in a register.

## LC3 - Review Addressing modes

Sign-extend (SX), by replicating the most significant bit as many times as necessary to extend to the word size of 16 bits.

c + SX(offset9)]] = sr

## Exercise

### .ORIG x3000

- LD R1, LABEL

- LDI R2, LABEL

- LDR R3, R2, #1

- LEA R4, LABEL

- LABEL .FILL x4001

- .END

### Assume

| ; | x4001 | x6001 |

|---|-------|-------|

| ; | ••••• |       |

| ; | x6001 | x7001 |

| ; | x6002 | x7002 |

### What are the values of R1, R2, R3 & R4 at each step?

Answers

x4001

x6001

x7002

x3004

## Exercise

| <ul> <li>Write a program to perform the multiplication 5 x 4.</li> </ul> | .ORIG x300<br>; R0 - out<br>; R1 - mul<br>; R2 - loo |

|--------------------------------------------------------------------------|------------------------------------------------------|

| <ul> <li>Need a way to store 5 and 4 as<br/>arguments</li> </ul>         | AND R0, R0<br>AND R1, R1<br>AND R2, R2<br>ADD R1, R1 |

| <ul> <li>There is no multiplication operation</li> </ul>                 | ADD R2, R2<br>LOOP BR:<br>ADI                        |

| <ul> <li>So have to repeat addition</li> </ul>                           | ADI<br>BR                                            |

|                                                                          | DONE HALT<br>.END                                    |

```

00

tput, init to 0

ltipicand 1, init to 5

op counter, init to multiplicand 2

0, #0

1, #0

2, #0

1, #5

2, #4

Rz DONE

DD R0, R0, R1

DD R2, R2, #-1

R LOOP

```

## LC3 - Review Pseudo-ops

- Looks like instruction but the "opcode" starts with a dot.

- Assembler instructions/directives that make our lives easier.

| Opcode   | Operand            |                            |

|----------|--------------------|----------------------------|

|          |                    |                            |

| .ORIG    | address            | Starting a                 |

| .END     |                    | En                         |

| .BLKW    | n                  | Allocate                   |

| .STRINGZ | n-character string | Allocate n+1<br>characters |

### Meaning

- address of program

- nd of program

- n words of storage

- locations, initialize with s and null terminator

### Figure C.1 - P&P 3rd Ed.

### Figure C.3 - P&P 3rd Ed.

# Textbook v2 vs. v3

- What is different in v3 compared • What does that mean for you? to v2?

- LEA no longer sets condition codes

- TRAP instructions do not store linkage in R7

This probably doesn't mean much to you right now

- Do MPS on EWS machines

- Practice for the quiz on the online simulator: <u>https://</u> courses.grainger.illinois.edu/ ece220/sp2020/lc3web/ index.html

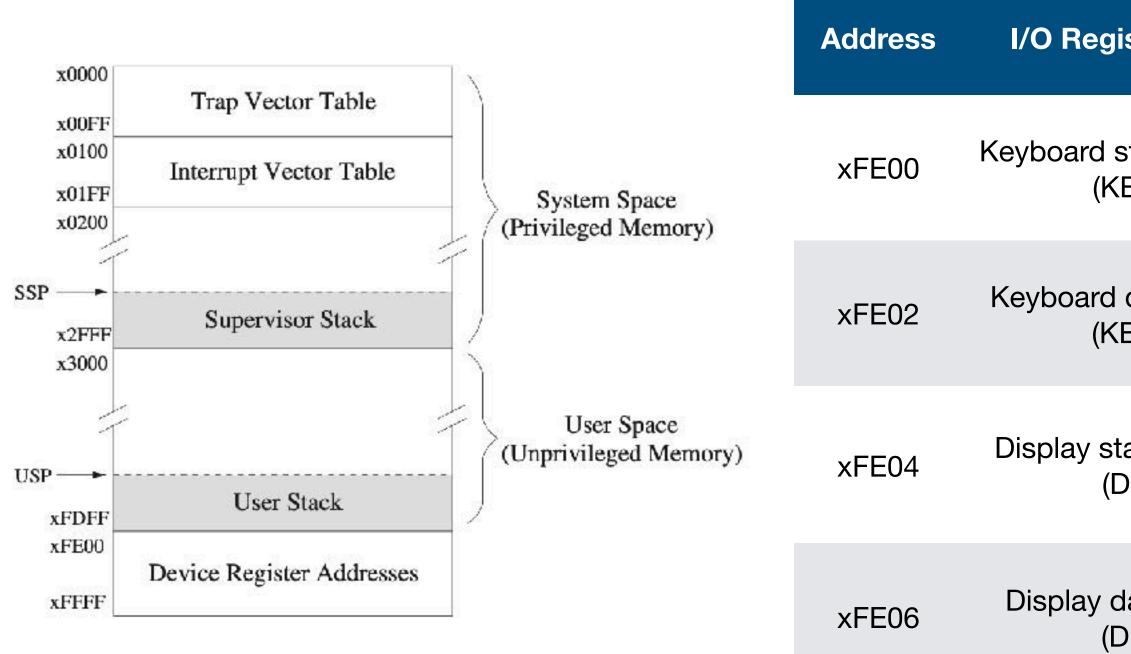

# Memory mapped I/O

- How do we communicate with the computer?

- Memory-mapped I/O: Hardware devices (i.e. their registers) are treated the  $\bullet$ same as the computer's main memory and addressable the same way

- Memory of *peripherals* is *physically* separate from main memory

- Alternative: Port mapped I/O (requires having more specialized) instructions)

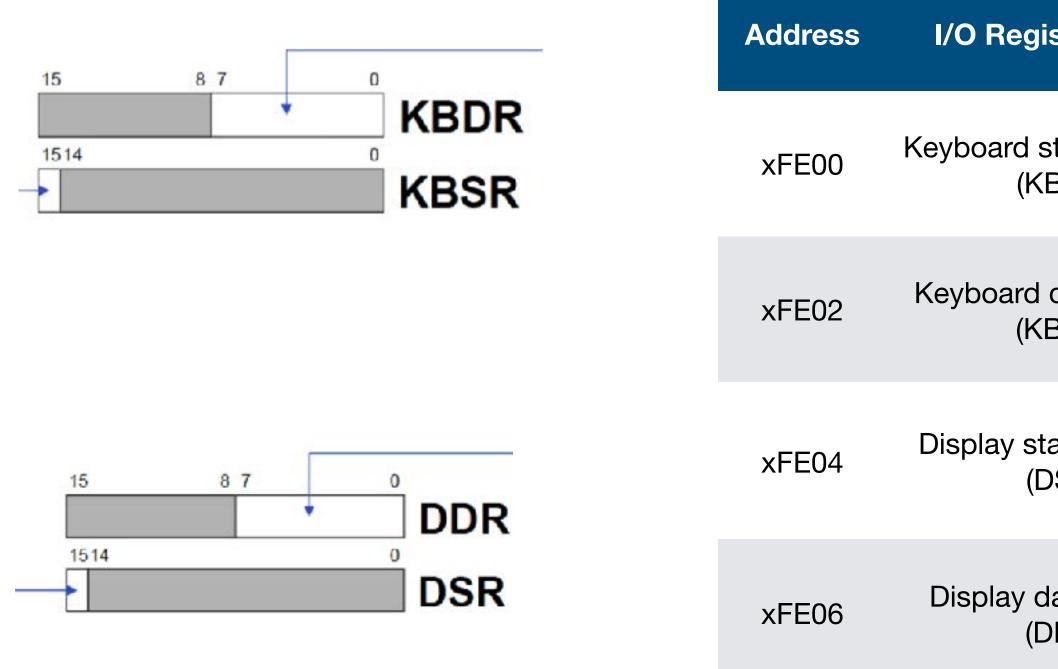

- In LC3: KBDR, KBSR, DSR, DDR are used for [K]eyboard and [D]isplay respectively.

# LC3 - Input/Output (IO)

Figure A.1 - P&P 3rd Ed.

| ister Name              | I/O Register Function                                                                                                         |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| status register<br>BSR) | The ready bit (bit[15]) indicates<br>if the keyboard has received a<br>new character                                          |

| data register<br>BDR)   | Bits [7:0] contain the last<br>character typed on the<br>keyboard                                                             |

| atus register<br>DSR)   | The ready bit (bit[15]) indicates<br>if the display device is ready to<br>receive another character to<br>print on the screen |

| data register<br>DDR)   | A character written in bits [7:0]<br>will be displayed displayed on<br>the screen                                             |

# LC3 - Input/Output (IO)

| ister Name              | I/O Register Function                                                                                                         |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| status register<br>BSR) | The ready bit (bit[15]) indicates<br>if the keyboard has received a<br>new character                                          |

| data register<br>BDR)   | Bits [7:0] contain the last<br>character typed on the<br>keyboard                                                             |

| atus register<br>DSR)   | The ready bit (bit[15]) indicates<br>if the display device is ready to<br>receive another character to<br>print on the screen |

| data register<br>DDR)   | A character written in bits [7:0]<br>will be displayed displayed on<br>the screen                                             |

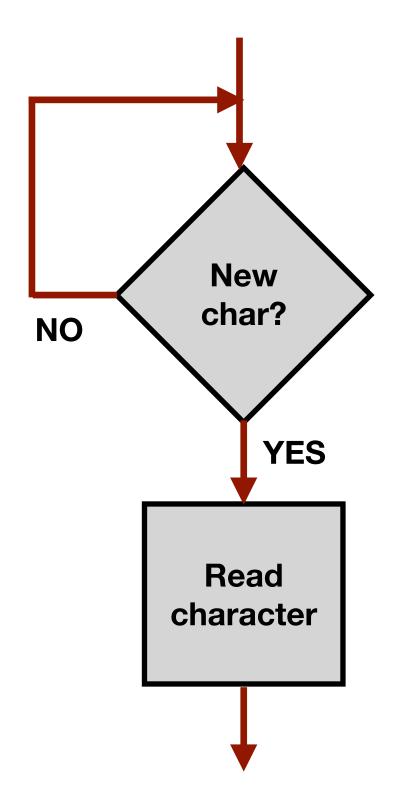

### LC3 - Input from keyboard **Basic routine** Handshaking is performed using KBSR & KBDR

- When user presses a key

- Its ASCII code is placed in **KBDR**[0:7]

- **KBSR**[15] is set to 1 (ready bit)

- Keyboard is disabled, i.e., any further keypress is ignored

- When **KBDR** is read by CPU

- KBSR[15] is set to 0

- Keyboard is enabled

## LC3 - Input from keyboard Basic routine

.ORIG x3000

;Create a loop to check KBSR

;If ready bit unset loop again

;If ready bit set, read KBDR into R0

KBSR .FILL xFE00

KBDR .FILL xFE02

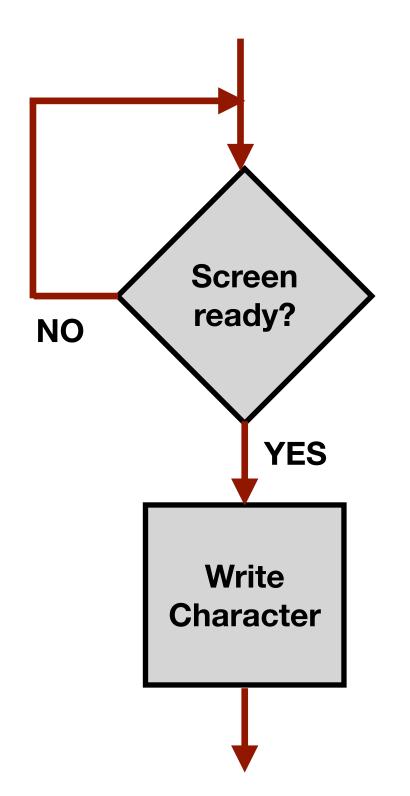

### LC3 - Display to console **Basic routine** Handshaking is performed using DSR & DDR

- When display is ready to present a character

- DSR[15] is set to 1 (ready bit)

- When a new character is written to DDR

- DSR[15] is set to 0

- Any other chars written to DDR are ignored

- DDR[7:0] is displayed

## LC3 - Display to console Basic routine

.ORIG x3000

;Create a loop to check DSR

;If ready bit unset loop again

;If ready bit set, write R0 into DDR

DSR .FILL xFE04 DDR .FILL xFE06

## Exercise

- .ORIG x3000 • Write a program to display "ECE 220 is fun!" to the DPOLL console. You can use the BRzp DPOLL pseudo-op .STRINGZ to STI R0, DDR store string to memory. Do BRnzp CHRLOOP not use TRAP codes (if you ALLDONE HALT know what they are). DSR .FILL xFE04

- DDR .FILL xFE06

.END

LEA R2, MY STRING CHRLOOP LDR R0, R2, #0 BRz ALLDONE LDI R1, DSR

ADD R2, R2, #1

MY STRING .STRINGZ "ECE 220 is fun!"

## **Issues**?

- Limited amount of GPRs polling display & keyboard uses up two of them

- Code often repeated inefficient to keep inserting same code over • & over again

- Human error keeping track of registers & having direct access to hardware registers is recipe for unforced errors & bugs

# Solution?

- Subroutines & repeated code

- Also called *functions*

- TRAP routines

- More next time