Shashank Vaidehi Mahesh - ECE 120

Manav Agrawal - ECE 120

Aman Sekhon - ECE 120

Statement of Purpose:

Our purpose is to develop a system that would be able to simulate a modern traffic light using an FPGA and a machine learning algorithm. An FPGA(Field Programmable Field Array) is a type of integrated circuit that contains a bunch of logic blocks. These blocks are able to be programmed to represent different logic functions. This allows for a lot of variation in electronic functionality making it very useful to this project.

For example, the algorithm could take typical traffic congestion and the importance of the road(major roadway vs a small inner road) to determine how much time to allot to a red light vs a green light. This would allow the traffic light to generate information on the duration of each traffic state without always needing human instruction. This would be done by using sensors that return data directly about certain aspects of traffic to generate an approximation of relative congestion.

Design Details:

System Overview:

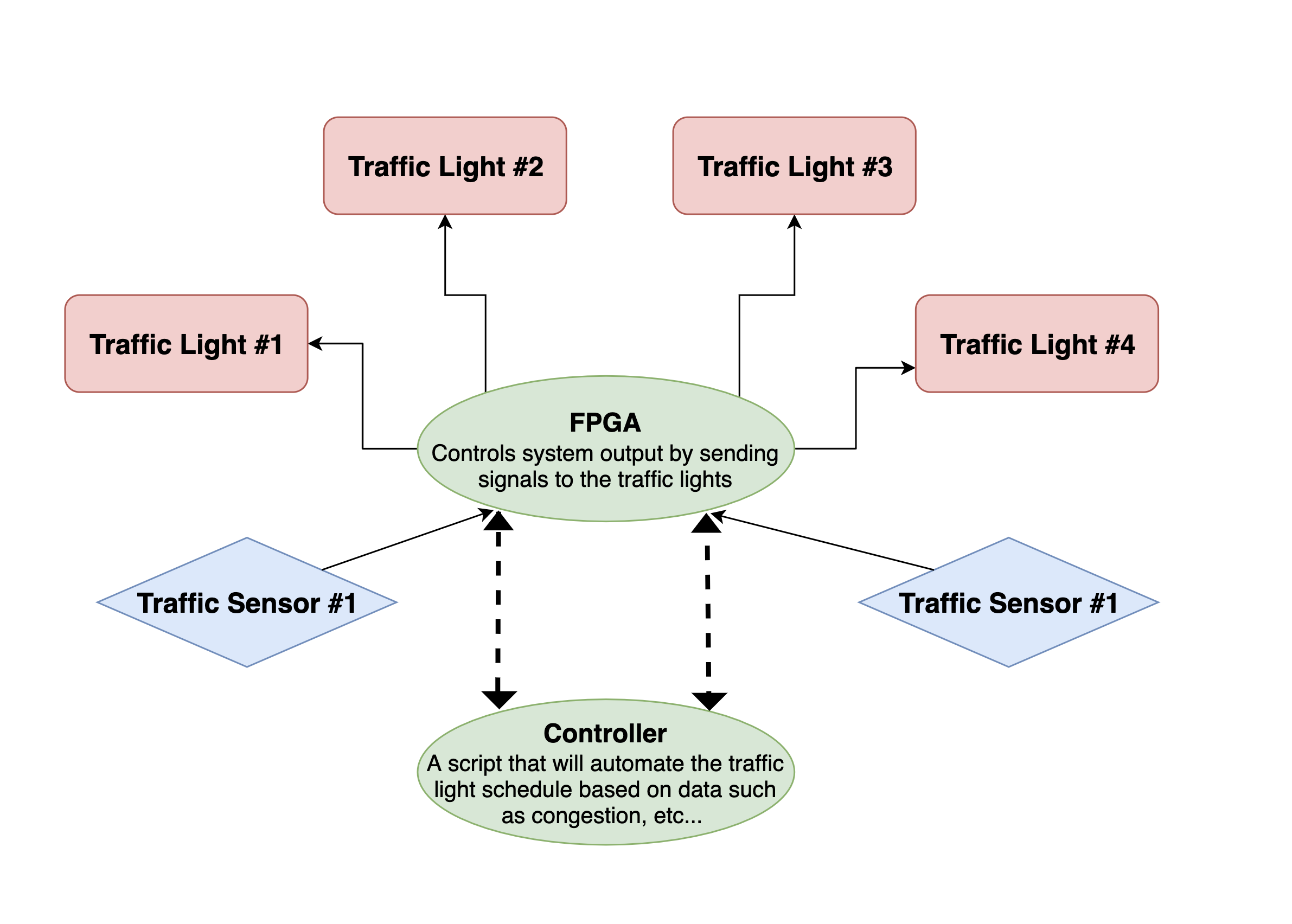

This system is built to control a traffic light system. A controller will interact with the FPGA, which will directly control the Traffic light system. The controller will be abstracted from the FPGA, and thus, any timing pattern could be used to control the traffic system. We will be using an algorithm that uses a minimum delay based on the hour of the day. The purpose of this is to eliminate unnecessary wait time during non-traffic hours.

We will be presenting a small-scale model on a breadboard, and we will use an FPGA to control the traffic lights and read data from the sensors. In our model, we will be using tactile switches as a “tally count” for the number of cars in a lane at the intersection, and LED’s to model the traffic lights.

Parts and Materials Required:

LED’s (for traffic lights)

IR Sensors (Lane and Approach sensors to measure the lane density)

Tactile button switches

FPGA (Field Programmable Gate Arrays) Type: SRAM FPGAs

Looking into Spartan FPGA Development Boards

Possible Challenges:

Using and understanding Verilog HDL or other similar Hardware description languages to simulate and create an algorithm to manage traffic congestion.

Creating a schematic of the proposed traffic control system on software such as Altera

Implementing the FPGA Logic gates to understand the simulated results and process using the LEDs on FPGA boards

References:

FPGA-Based Advanced Real Traffic Light Controller System Design - IEEE Conference Publication, ieeexplore.ieee.org/abstract/document/4488383.

Holambe, Shilpa U., and D. B. Andore. “[PDF] Traffic Light Control System Based on FPGA - Semantic Scholar.” [PDF] Traffic Light Control System Based on FPGA - Semantic Scholar, www.semanticscholar.org/paper/Traffic-Light-Control-System-Based-on-FPGA-Holambe-Andore/9803e384407a6a7326a5a75ae7aa63d77055472b#paper-header.

http://www.iosrjournals.org/iosr-jece/papers/Vol.%2012%20Issue%205/Version-2/B1205020713.pdf - Online Journal which has simulated a similar Traffic intersection through FPGA

Ortiz, José Elías García, and Robert H. Klenke. “Simple Traffic Light Controller: A Digital Systems Design Project - Semantic Scholar.” Semantics Scholar, 1AD, www.semanticscholar.org/paper/Simple-traffic-light-controller%3A-A-digital-systems-Ortiz-Klenke/cbb27b67c57e54078df16d0cdeb0ccc41aabdfda#paper-header.

Attachments:

Comments:

|

I would recommend one of the small FPGAs paired with an ARM core rather than a just FPGA board (they make one that is a USB stick for easy programming). You'll likely not need many LUTs and having a hardware µC core will make your lives easier. You're off to a great start! Don't forget to ask TAs if you have any questions. |

|

I would honestly recommend not going with an FPGA for this project. I would look into the Intel Neural Compute Stick https://www.amazon.com/Intel-Neural-Compute-Stick-2/dp/B07KT6361R/ref=asc_df_B07KT6361R/?tag=hyprod-20&linkCode=df0&hvadid=320048880417&hvpos=1o2&hvnetw=g&hvrand=17625253716783409540&hvpone=&hvptwo=&hvqmt=&hvdev=c&hvdvcmdl=&hvlocint=&hvlocphy=9022196&hvtargid=pla-628439506973&psc=1&tag=&ref=&adgrpid=61389685902&hvpone=&hvptwo=&hvadid=320048880417&hvpos=1o2&hvnetw=g&hvrand=17625253716783409540&hvqmt=&hvdev=c&hvdvcmdl=&hvlocint=&hvlocphy=9022196&hvtargid=pla-628439506973 Trying to do an FPGA AI accelerator as a single semester project may be very difficult. |