| Name | NetID | Section |

|---|---|---|

| Joshua Yun | jjyun4 | ECE 120 |

Statement of Purpose

The purpose of this project is to explore how floating point numbers are operated on in a CPU, as well as how different parts of the CPU signal each other to pass information and commands between different parts.

With this project, the implementation will also require me to gain practical experience with either System Verilog or Verilog, allowing me to use those in other projects in the future.

Background Research

I have been interested in how some of the higher functions of modern CPUs have been implemented, and this would be a great stepping stone into that field.

I have looked at some simpler CPUs for reference such as the 8008, Z80, and basic implementations of other CPUs from other classes similar to ECE 120

Floating point numbers will be using IEEE 32 bit notation, with all the bits in memory being stored in 8 bit or 16 bit chunks so that the cpu can work with them when sending the values to the accelerator.

Output can be done with bit banging an SPI connection in the FPGA and talking with the arduino for output.

Block Diagram / Flow Chart

System Overview

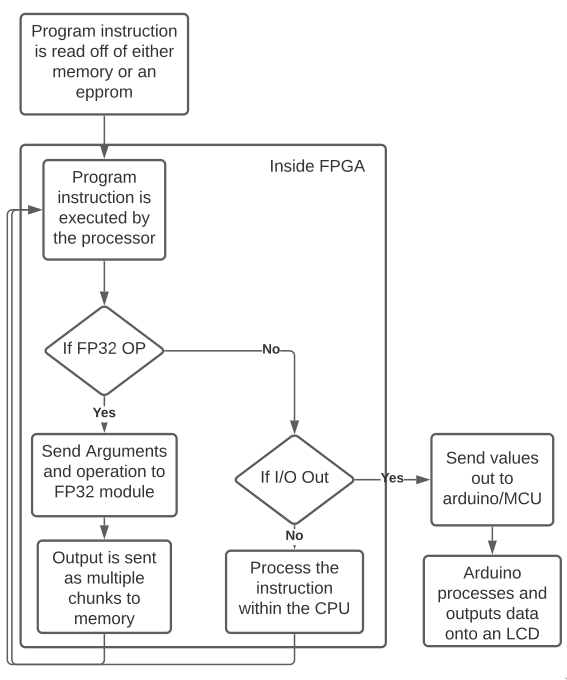

The block diagram is representative of an example program being processed through the FPGA.

This system is modeled after the Harvard architecture, where the program instructions will be prewritten EEPROM modules with the program values being stored onto a memory module built directly onto the FPGA, though this may change in the future if more knowledge is gained on how to store memory in the FPGA.

The ISA will be modeled after LC3, with extensions being made for the floating point operations in question.

The Instructions will be stored either in memory on on a 28C16 EEPROM for access and initially set to all zero with the exception of the program, and since the LC3 NOP is 0x0000, the program will run nop unless encountering a program.

All outputs of the computer that need to be displayed will take the form of a char and processed into SPI bits, which will then be used to communicate with the Arduino, i.e. through bit banging, at which point the Arduino will print out the chars on the LCD screen.

The CPU will be simulated on verilator before any testing is done on the actual FPGA to ensure that the code is somewhat working before being tested on the FPGA.

Parts

16x2 LCD Screen with link to Mouser for $13.90 qty 1 or through the ECE in house supplier using a Spark Fun SerLCD

28C16A EEPROMS with link to Jameco for 5.49 qty 2

Arduino Nano from the Parts list for $10.00 qty 1

Breadboard are not necessary (Have the ECE 120 Bread board kit)

Wires are not necessary (Have the ECE 120 Wiring kit)

FPGA not necessary (In possession of a Orange Crab 25K LUT FPGA)

Total budget: 34.88

Possible Challenges

Being able to output binary data that is readable for the MCU as well as outputting that data through the microcontroller.

Learning verilog to the point where I can write an efficient microcontroller in Verilog onto the FPGA.

Debugging the FPGA's code if something is wrong and without an obvious problem or solution.

References

[1]"Verilog, Formal Verification and Verilator Beginner's Tutorial", Zipcpu.com, 2021. [Online]. Available: https://zipcpu.com/tutorial/.

[2]B. Prashanth, P. Kumar and G. Sreenivasulu, "Design & implementation of floating point ALU on a FPGA processor", 2012 International Conference on Computing, Electronics and Electrical Technologies (ICCEET), 2021 [Online]. Available: https://ieeexplore.ieee.org/document/6203790.

[3]D. Sorin, Arithmetic and ALU Design. Beaufort: Duke University, 2021 [Online]. Available: http://people.ee.duke.edu/~sorin/prior-courses/ece152-spring2011/lectures/3.3-arith.pdf.

[4]P. Shengale, V. Dahake and M. Mahendra, "Single Precision", International Research Journal of Engineering and Technology, vol. 2, no. 2, 2015 [Online]. Available: https://www.irjet.net/archives/V2/i2/Irjet-v2i2135.pdf.

[5]B. Ozkilbac and T. Karacali, "Implementation and Design of 32 Bit Floating-Point ALU on a Hybrid FPGA-Arm Platform", Journal of Brilliant Engineering, vol. 2, 2021 [Online]. Available https://www.acapublishing.com/dosyalar/baski/BEN_2019_16.pdf

Final Report: Click_Here

Video: Click_Here