| NAME | NETID | COURSE |

|---|---|---|

| Angelo Santos | angelos4 | ECE120 |

| Saichara Bandikallu | sb35 | ECE 120 |

- Introduction

Statement of Purpose

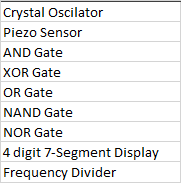

The purpose of this project is for a learning experience. We will be working from the ground up to try and develop a chess clock using a circuit board, a Crystal oscillator for frequency and a piezoelectric sensor for the inputs.

Background Research

The background research we have done for this project was by looking for the individual components and finding different guides for developing the circuit. This circuit will be using knowledge from separate areas of electrical and computer engineering to code using logic gates on the circuit board. We will also be using knowledge from ECE 110 to figure out how to change an analog to a digital signal. This project is important because it will allow us to work on the skills that we have learned/ are learning in our ECE 110 and 120 class. This project will allow us to design a basic circuit and use logic gate chips for the combinational logic. When we were researching projects, we came across a clock design. A normal clock, however, seemed too simple, but it seemed like a good project where we could learn a variety of skills. Therefore, by making a chess clock timer, we could put a twist on a regular clock/counter. We also noticed that many of the clocks that are made online, use premade chips that already have a clock function. This is why we decided to make the crystal oscillator circuit and the logic behind it ourselves. We believe this will provide a challenge that will be a good learning experience that relates to our studies. - Design Details:

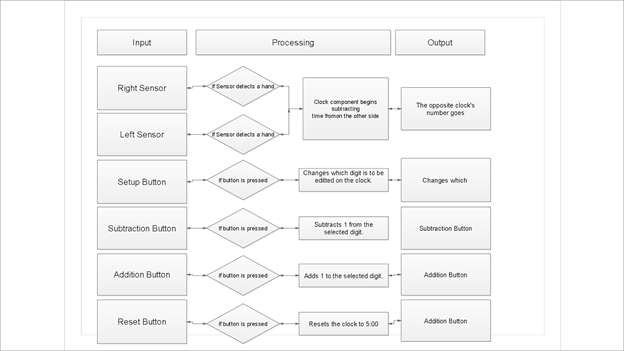

b. Block Diagram / Flow Chart'

a. System Overview

This block diagram describes the outcomes that will come when each of the buttons within the project are pressed. Something that is not mentioned within the block diagram is the way that the timer will work and how it will interact with the FPGA board. However, these are the inputs that will actually be interacted with. - Parts

4. Possible Challenges

We might run into some problems with trying to code the 7-segment display, as it is also new to us. Other challeges well run into are ensuring the frequency of the crystal stays at 1 hertz and managing all the logic gates on the board so they properly calculate the time.

5. References

- [1]2020. [Online]. Available: https://www.electronics-tutorials.ws/oscillator/crystal.html. [Accessed: 15- Feb- 2020].

- [2]"FPGA (Field Programmable Gate Array) : Architecture and Applications", WatElectronics.com, 2020. [Online]. Available: https://www.watelectronics.com/fpga-architecture-applications/. [Accessed: 15- Feb- 2020].

- [3]"Module 914: Digital-to-Analog Converter", Courses.engr.illinois.edu, 2010. [Online]. Available: https://courses.engr.illinois.edu/ece110/sp2020/content/labs/Modules/Modules_914_DAC_v1.pdf. [Accessed: 15- Feb- 2020].

- [4]“Digital Clock,” Engineer Without Fear. [Online]. Available: http://engineerwithoutfear.com/project_EEIclock.html. [Accessed: 21-Feb-2020].

Attachments:

Comments:

|

Great project. Please add your team description. |

|

It looks like you've done your research; but I'm going to say that using an FPGA for this is going to unnecessarily complicate things. If you haven't used an FPGA before, there is going to be a huge learning curve to getting started with SystemVerilog and common FPGA toolchains. It is also comically expensive for the kind of application you're using it for. FPGAs are primarily used for complex, realtime, low-latency applications that require large data throughput, wide bandwidths, and other domain-specific advantages to FPGAs. I would reconsider using FPGAs for this project. If you are dead-set on using an FPGA, I am warning you it will require MANY hours of independent learning, far outside the scope of this lab. There is one other team pursuing FPGAs, and the lead student on that team is actually auditing ECE 385 and attending those lectures and using 385 lab kit in order to accomplish this. If you're willing to put in equivalent effort (multiple hours per week of independent learning) this will be doable. If not, I would use another technology instead of an FPGA. |

|

I agree with Finn and also double check a lot of the functionality in already existing chess clocks as they may give you ideas for how you want to best utilize you buttons/sensors in relation to your logic. There's a lot of possible depth in this project which is great (updating the block diagram for yourself during the project may be of benefit) but I would just try to iron out details ASAP. |

|

As mentioned, FPGA is overkill. That being said, I also think it would be valuable to learn. Your choice "Also, we might run into some problems with trying to code the 7-segment display, as it is also new to us." If you do it pin by pin, you may have a bad time. Try a <https://www.electronics-tutorials.ws/combination/comb_6.html> decoder |

|

Please add additional background research and a list of the students working on this project. Please make these revisions before tonight. Your proposal is not yet approved. |

|

We updated our proposal last week Friday, is there anything else you would like us to change? |