| Name | NetID | Section |

|---|---|---|

| Deepika Batra | dbatra3 | ECE 110 |

| Bryan Zhang | bryanxz2 | ECE 110 |

Project Proposal

Statement of Purpose

The purpose of our project is for us to get a ground-up understanding of how computers work, all the way from the transistors to a simple output being displayed. The input is a pseudo-keypad made from photoresistors and analog to digital converters, which will feed into a small scale computer that does the required calculations and stores it in a RAM/displays it with LEDs.

Background Research

Please provide details on the background research your group has done for your project. Explain what drives you to work on this project and/or why this project is important. Also include discussions on any similar projects your group have looked at in coming up with your project. How is your proposed project different or similar to those your group have looked at.

Our motivation behind this project is a desire for a fundamental understanding of computers and CPUs, which we believe is crucial for any electrical or computer engineer. We did some initial research using eater.net, a website created by a guy who built his own 8-bit computer. We also drew inspiration from a couple of previous years' projects including the 16 bit CPU the 8 bit emulated computer. Our goal here is to use the most basic components, which would include some IC's at the most complex level, to construct a working computer to interpret data.

Block Diagram / Flow Chart

System Overview

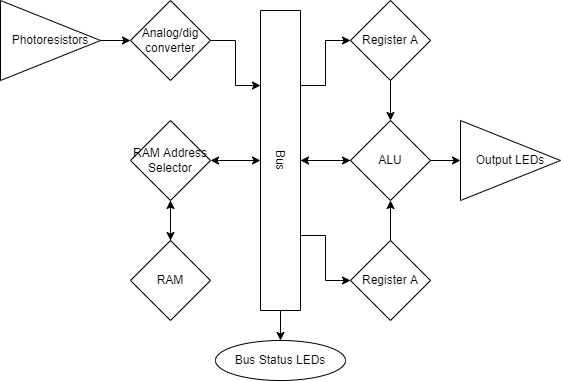

The input to the system begins with a few photoresistors that will represent binary input. In order to convert it to digital signals, we will use an analog to digital converter. These inputs will arrive at the input register, which will be instructed to be copied into the ALU or the RAM via the bus (8 bit). From there, the ALU will perform a simple arithmetic operation (add or subtract) using the two numbers, and will either store it into the RAM or hand it over to the output register to be displayed. Here, the instruction counter tells the ALU the right operation to be performed, and the control logic unit makes sure the bus stays non-congested (i.e. components aren't trying to load information simultaneously onto the bus) and that the right operations are being loaded into the ALU/instruction counter. Finally, the clock will keep everything synchronized (we'll probably be using a 555 module). This is only a tentative design as we don't yet have a full understanding of the architecture of the system, but this is how we believe it will work.

NOTICE: We weren't able to build the entire system, see report for details on final product

Parts

We retrieved this list from eater.net. This is a tentative list and is subject to change once we have a better understanding of the system.

| Name | Model | Qt | Vendor | Price |

|---|---|---|---|---|

| Breadboards | 1286-1220-ND | 3 | Digikey https://www.digikey.com/en/products/detail/digilent-inc/340-002-1/9556131 | $24.99 |

| 555 timer IC | 27423 | 4 | Jameco | 0.69 |

| 74LS00 (Quad NAND gate) | 46252 | 2 | Jameco | 1.09 |

| 74LS02 (Quad NOR gate) | 46287 | 1 | Jameco | 0.65 |

| 74LS04 (Hex inverter) | 46316 | 5 | Jameco | 0.69 |

| 74LS08 (Quad AND gate) | 46375 | 3 | Jameco | 0.69 |

| 74LS32 (Quad OR gate) | 47466 | 1 | Jameco | 0.69 |

| 74LS86 (Quad XOR gate) | 47466 | 1 | Jameco | 0.49 |

| 74LS107 (Dual JK flip-flop) | 46412 | 1 | Jameco | 1.95 |

| synchronous binary counter 4-bit | 46818 | 2 | Jameco | 0.89 |

| 74LS173 (4-bit D-type register) | 46922 | 8 | Jameco | 01.49 |

| 74189 (64-bit random access memory) | 49883 | 2 | Jameco | 4.95 |

| 28C16 EEPROM | 74691 | 3 | Jameco | 5.49 |

| Double-throw toggle switch | 2258831 | 3 | Jameco | 0.69 |

| Momentary 6mm tact switch | 149948 | 3 | Jameco | 0.35 |

| 74LS283 (4-bit binary full adder) | 47423 | 2 | Jameco | 1.49 |

| 74LS138 (3-to-8 line decoder) | 46607 | 1 | Jameco | 0.79 |

| 74LS139 (Dual 2-line to 4-line decoder) | 46623 | 1 | Jameco | 0.79 |

| 74LS157 (Quad 2-to-1 line data selector) | 46771 | 4 | Jameco | 0.79 |

| 74LS161 (4-bit synchronous binary counter) | 46818 | 2 | Jameco | 0.89 |

| 74LS245 (Octal bus transceiver) | 47212 | 6 | Jameco | 0.89 |

| 74LS273 (Octal D flip-flop) | 47386 | 1 | Jameco | 0.85 |

| 8-position DIP switch | 38842 | 1 | Jameco | 0.75 |

| 4-position DIP switch | 38820 | 1 | Jameco | 0.75 |

| Assorted LEDs | TBD | TBD (>50) | TBD | TBD |

Possible Challenges

We are building a computer from scratch without much prior knowledge, so our understanding of CPU architecture is limited. Debugging may also be a challenge due to the lack of any software.

References

[1]B. Eater, "Ben Eater", Eater.net, 2021. [Online]. Available: https://eater.net/. [Accessed: 17- Sep- 2021].

Final Deliverables

Video

Report

Calculator From Scratch

Bryan Zhang

Deepika Batra

University of Illinois at Urbana Champaign

ECE 110 Honors Lab

December 5, 2021

Introduction

The goal for this project was to design and build an 8-bit calculator from basic integrated circuit components including logic gates, registers, memory, etc. Through this effort we hoped to establish a solid understanding of basic CPU architecture, learn the ins and outs of designing and building a sophisticated circuit, and practice our debugging and troubleshooting skills on a large system that runs on zero software.

Design

The original design of this project was a programable, autonomous calculator that could take in inputs from the photoresistor array as both the data (to be operated upon) and the instructions themselves. From there, the instruction counter and control logic as well as the clock would carry out the functions in the correct sequence and achieve an output automatically (refer to Block Diagram / Flow Chart section for full circuit flowchart). This, however, was not achieved, and instead, the project was downscaled through the removal of the clock module, program counter, control logic unit as well as a few ancillary subcircuits.

The resulting product consists of a photoresistor input, two registers, a RAM, RAM address selector module, the arithmetic logic unit (8 bit full adder), and the bus. Thus, the system requires manual operation, and the diagram below shows the final design flowchart:

Here, the input operation remains the same with photoresistors placed as the second resistor in simple voltage dividers. The output is fed into an AND gate with its other output tied to 5V. This essentially acts as an analog to digital converter (i.e., when the voltage being put into the AND gate is high enough, the AND output is a constant high), and thus, data can be written into the RAM in a punch card-like manner. Bus transfers, however, need to be manually conducted by pulsing the read and write (and clock for the registers) pins on the RAM and registers.

Results

Our final circuit consists of six major components, as shown in the above diagram, resulting in an 8-bit calculator-esque design capable of storing 16 bytes of information (easily expandable to 32K) and adding or subtracting any two 8-bit integers with carry functionality. The operations, however, must be conducted manually through button presses and wire placements.

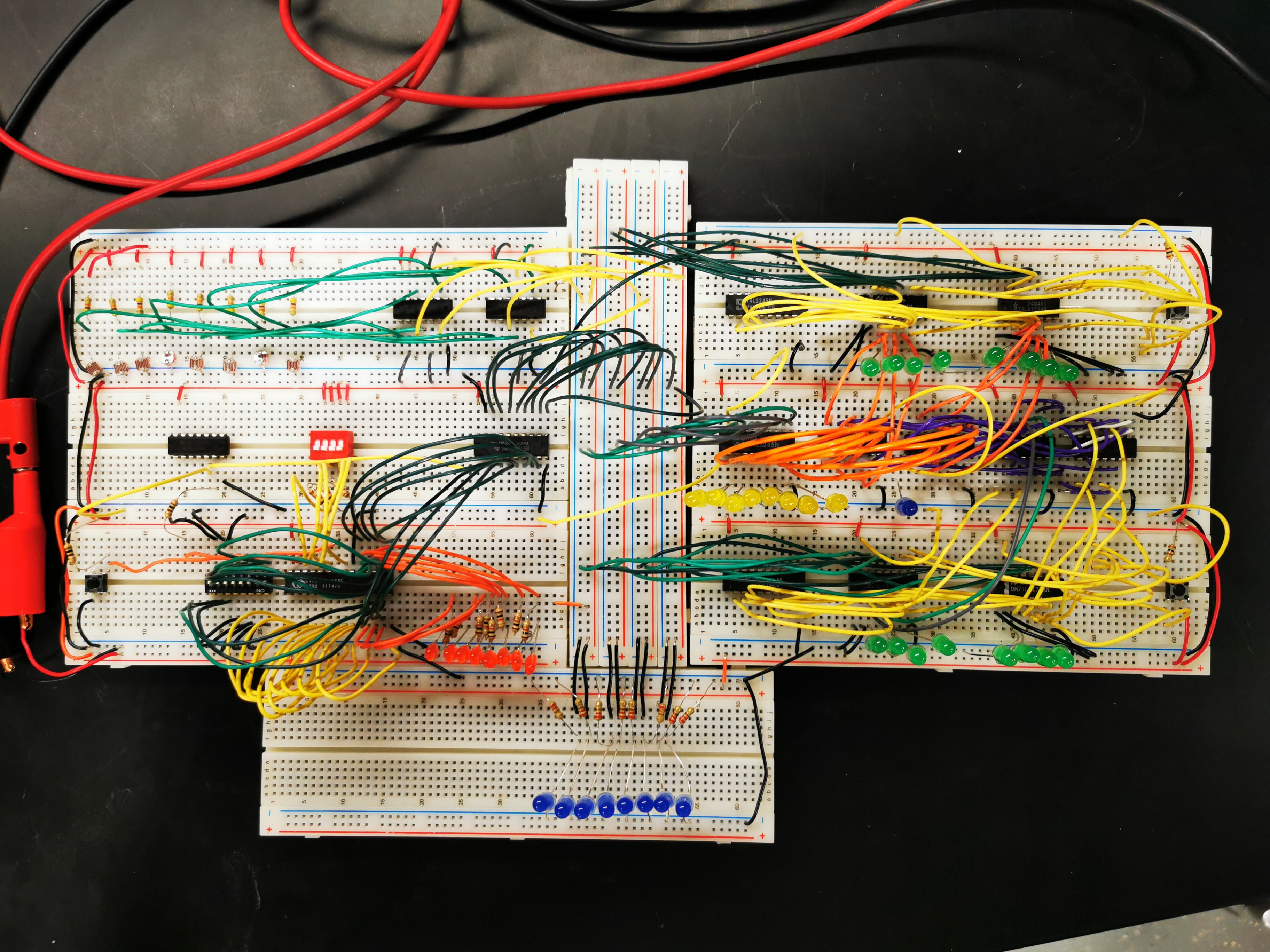

The modules in counterclockwise order starting from the top left are: photoresistor input, RAM address selection and read/write selection, RAM (8-switch dip switch was only used for testing), bus display, register B, ALU, register A, bus.

The process begins with a byte of information generated by covering a set of photoresistors of our choosing via the input module. This byte then gets sent onto the bus, from which any other component can read. Next, the RAM module (cy7c199-12pc) reads the information from the bus through a 74LS245 octal bus transceiver, which can be set to both bus-to-module mode and module-to-bus mode. From there, a button on the RAM module can be pressed to store the byte into a preselected address (4-switch dip switch). The process repeats for whatever data needs to be programmed on the RAM.

Afterwards, the RAM is set to its read mode, where the data from a specific address is fed into the RAM bus transceiver, and with the bus transceiver’s direction pin set to module-to-bus (Ax to Bx through the DIR pin), the data from the RAM can then be displayed on the bus.

Assuming all the data required is already stored in the RAM, the next step is to load the relevant data onto the A and B registers (74LS173), which is achieved by reading the first byte from the bus and writing it onto A and reading another byte and writing it onto B.

Finally, the data from the two registers are directly connected to the input of the ALU module. Register A is connected directly to the A inputs of two four-bit full adders with carry I/O (74LS283). However, register B is connected first to the A inputs of two quad XOR gates (74LS86), totaling a byte, and the output of the XOR gates are connected to the B inputs of the full adder. The reason for this intermediate step is to enable subtraction operations on the calculator. By turning the XOR gates’ B inputs to high, the output is the inverted B register data. This gives the one’s complement of the B register. Next that same wire that indicates subtraction to the XOR gates is also connected to the carry-in of the first 4-bit adder, which results in a two’s complement of register B added to the data from register A, yielding a successful subtraction. Addition can be simply carried out by setting the subtract pin to low.

After the operation on the ALU, the output data can be inserted onto the bus via another bus transceiver connected to the ALU, and thus results can be stored back into the RAM or into a register for further operations.

Problems and Challenges

The main challenge we faced while completing this project was our lack of knowledge of CPU architecture as well as our limited experience working with integrated circuit chips. This forced us to spend a considerable amount of time doing research, watching videos (Ben Eater’s channel), and reading articles about how different parts of a computer worked on a fundamental level as well as the different logical components are laid out. Because of this and the time constraints, we were forced to downscale the project significantly in order to still produce a working product. Because of that, we ended up not following Ben Eater’s wiring schematics and designing a considerable portion of the computer from only referencing datasheets. Additionally, the 8-byte RAM modules were no longer in stock in the ECE eshop, but fortunately, we were able to find a suitable substitute, the cy7c199-12pc 32K RAM module. While it’s a lot more powerful than the 74LS189 RAM module detailed in Ben Eater’s guide, it was more difficult to operate. We eventually chose to only operate four of the fifteen address pins using a four-switch DIP switch, resulting in 16 bytes of usable RAM (easily expandable with more DIP switches).

Another challenge we faced was getting high enough voltage outputs from our ICs. Occasionally the output would be barely above two volts, resulting in fuzzy readings from our output LEDs. Finally, wire management turned out to be a time consuming issue as the number of wires required for this system was immense.

Future Plans

As a natural extension of this semester’s project, adding in the programmable instructions and clock system could be the next goal. This removes the need for manual operation, which will not only decrease chances of human error, but also teach us a lot more about instruction sets architecture. Additionally, adding in a more comprehensive input mechanism could be a good next step (e.g., a simple push button-based keypad) that can speed up the programming process considerably.

With the previous steps done, maybe a more complex computer could be the next step, with capabilities enabled by much more memory as well as more sophisticated instructions.

References

MANY TI, Fairchild, Cypress datasheets