# Circuits

Lecture 11 Uniform Circuit Complexity

Non-uniform complexity

- Non-uniform complexity

- P/1

Decidable

- Non-uniform complexity

- P/1

Decidable

- Non-uniform complexity

- P/1 ⊈ Decidable

- $> NP \subseteq P/log \Rightarrow NP = P$

- ⊗ NP ⊆ P/poly ⇒ PH =  $Σ_2$ P

- Non-uniform complexity

- P/1

Decidable

- olimits NP ⊆ P/poly olimits PH = olimits olimits PH = olimits olimits olimits PH = olimits o

- Circuit Complexity

- Non-uniform complexity

- P/1

Decidable

- ⊗ NP ⊆ P/log ⇒ NP = P

- olimits NP ⊆ P/poly olimits PH = olimits olimits PH = olimits olimits olimits PH = olimits o

- Circuit Complexity

- SIZE(poly) = P/poly

- Non-uniform complexity

- P/1

Decidable

- ⊗ NP ⊆ P/log ⇒ NP = P

- olimits NP ⊆ P/poly olimits PH = olimits olimits PH = olimits olimits olimits PH = olimits o

- Circuit Complexity

- SIZE(poly) = P/poly

- SIZE-hierarchy

- Non-uniform complexity

- P/1

Decidable

- ⊗ NP ⊆ P/log ⇒ NP = P

- ⋄ NP ⊆ P/poly ⇒ PH =  $Σ_2$ P

- Circuit Complexity

- SIZE(poly) = P/poly

- SIZE-hierarchy

- SIZE(T') ⊆ SIZE(T) if T=Ω(†2†) and T'=O(2†/†)

- Non-uniform complexity

- P/1

Decidable

- ⊗ NP ⊆ P/log ⇒ NP = P

- ⋄ NP ⊆ P/poly ⇒ PH =  $Σ_2$ P

- Circuit Complexity

- SIZE(poly) = P/poly

- SIZE-hierarchy

- SIZE(T') ⊆ SIZE(T) if T=Ω(†2†) and T'=O(2†/†)

- Most functions on t bits (that ignore last n-t bits) are in SIZE(T) but not in SIZE(T')

Uniform circuit family: constructed by a TM

- Uniform circuit family: constructed by a TM

- Undecidable languages are undecidable for these circuits families

- Uniform circuit family: constructed by a TM

- Undecidable languages are undecidable for these circuits families

- Can relate their complexity classes to classes defined using TMs

- Uniform circuit family: constructed by a TM

- Undecidable languages are undecidable for these circuits families

- Can relate their complexity classes to classes defined using TMs

- Logspace-uniform:

- Uniform circuit family: constructed by a TM

- Undecidable languages are undecidable for these circuits families

- Can relate their complexity classes to classes defined using TMs

- Logspace-uniform:

- An O(log n) space TM can compute the circuit

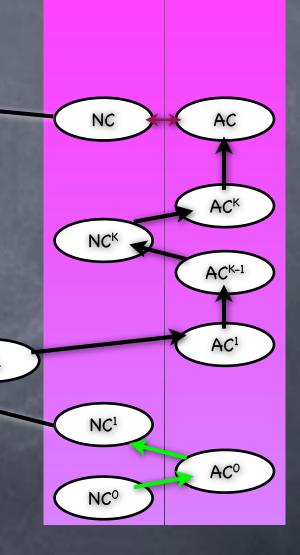

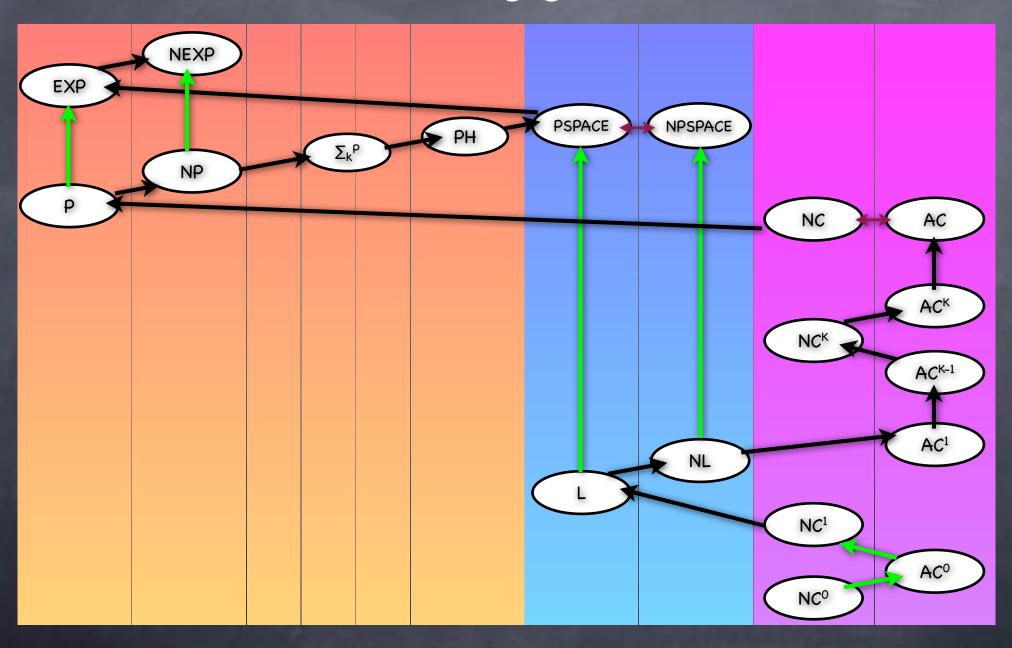

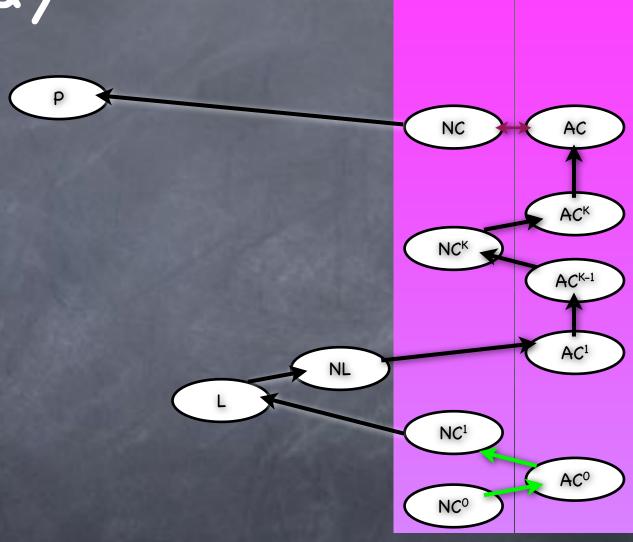

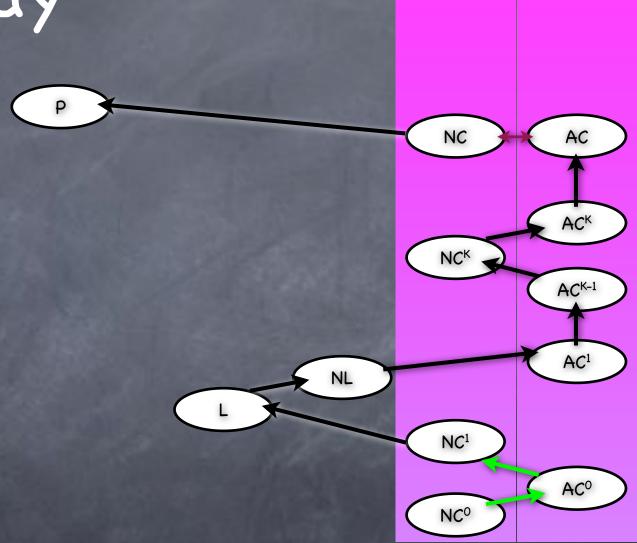

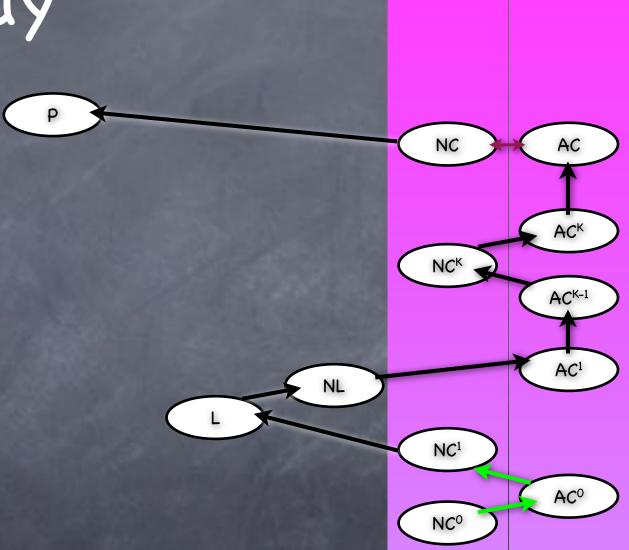

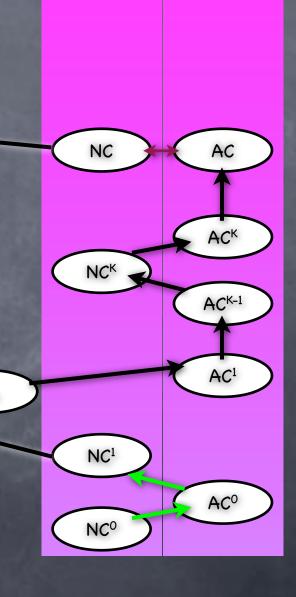

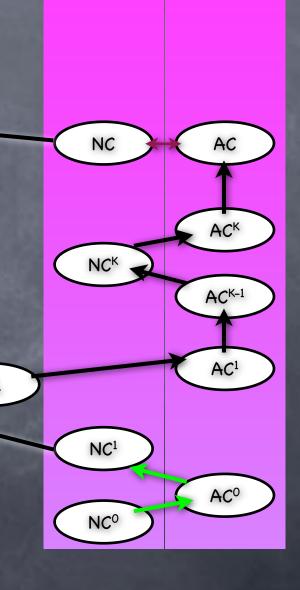

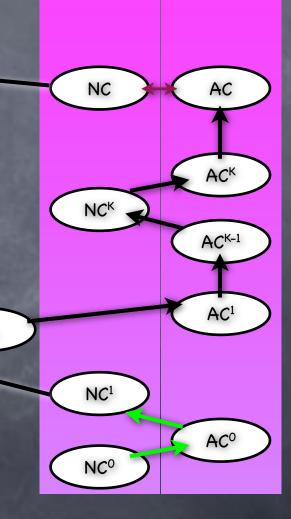

NCi: class of languages decided by bounded fan-in logspace-uniform circuits of polynomial size and depth O(logi n)

- NCi: class of languages decided by bounded fan-in logspace-uniform circuits of polynomial size and depth O(logi n)

- ACi: Similar, but unbounded fan-in circuits

- NCi: class of languages decided by bounded fan-in logspace-uniform circuits of polynomial size and depth O(logi n)

- ACi: Similar, but unbounded fan-in circuits

- NC<sup>0</sup> and AC<sup>0</sup>: constant depth circuits

- NCi: class of languages decided by bounded fan-in logspace-uniform circuits of polynomial size and depth O(logi n)

- ACi: Similar, but unbounded fan-in circuits

- NC<sup>0</sup> and AC<sup>0</sup>: constant depth circuits

- NC<sup>0</sup> output depends on only a constant number of input bits

- NCi: class of languages decided by bounded fan-in logspace-uniform circuits of polynomial size and depth O(logi n)

- ACi: Similar, but unbounded fan-in circuits

- NC<sup>0</sup> and AC<sup>0</sup>: constant depth circuits

- NC<sup>0</sup> output depends on only a constant number of input bits

NC =  $\cup_{i>0}$  NC<sup>i</sup>. Similarly AC.

- NC =  $\cup_{i>0}$  NC<sup>i</sup>. Similarly AC.

- NC =  $\cup_{i>0}$  NC<sup>i</sup>. Similarly AC.

- - $\odot$  Clearly  $NC^i \subseteq AC^i$

- NC =  $\cup_{i>0}$  NC<sup>i</sup>. Similarly AC.

- $OC^i \subseteq AC^i \subseteq NC^{i+1}$

- Olearly NC<sup>i</sup> ⊆ AC<sup>i</sup>

- $\circ$  NC =  $\cup_{i>0}$  NC<sup>i</sup>. Similarly AC.

- $OC^i \subseteq AC^i \subseteq NC^{i+1}$

- Clearly NC<sup>i</sup> ⊆ AC<sup>i</sup>

- So NC = AC

@ Generate circuit of the right input size and evaluate on input

- @ Generate circuit of the right input size and evaluate on input

- Generating the circuit

- @ Generate circuit of the right input size and evaluate on input

- Generating the circuit

- o in logspace, so poly time; also circuit size is poly

- @ Generate circuit of the right input size and evaluate on input

- Generating the circuit

- o in logspace, so poly time; also circuit size is poly

- Evaluating the gates

- @ Generate circuit of the right input size and evaluate on input

- Generating the circuit

- o in logspace, so poly time; also circuit size is poly

- Evaluating the gates

- Poly(n) gates

- @ Generate circuit of the right input size and evaluate on input

- Generating the circuit

- o in logspace, so poly time; also circuit size is poly

- Evaluating the gates

- Poly(n) gates

- Per gate takes O(1) time + time to look up output values of (already evaluated) gates

#### NC CP

- Generate circuit of the right input size and evaluate on input

- Generating the circuit

- o in logspace, so poly time; also circuit size is poly

- Evaluating the gates

- Poly(n) gates

- Per gate takes O(1) time + time to look up output values of (already evaluated) gates

- Open problem: Is NC = P?

Fast parallel computation is (loosely) modeled as having poly many processors and taking poly-log time

- Fast parallel computation is (loosely) modeled as having poly many processors and taking poly-log time

- Corresponds to NC (How?)

- Fast parallel computation is (loosely) modeled as having poly many processors and taking poly-log time

- Corresponds to NC (How?)

- Depth translates to time

- Fast parallel computation is (loosely) modeled as having poly many processors and taking poly-log time

- Corresponds to NC (How?)

- Depth translates to time

- Total "work" is size of the circuit

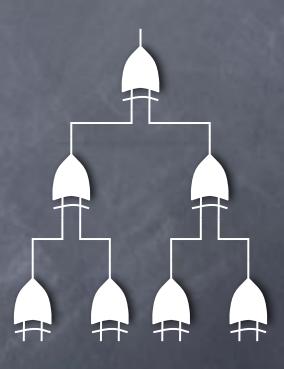

PARITY in NC¹

- PARITY in NC¹

- PARITY = { x | x has odd number of 1s }

- PARITY in NC¹

- PARITY = { x | x has odd number of 1s }

- Circuit should evaluate x₁⊕x₂⊕...⊕x<sub>n</sub>

- PARITY in NC¹

- PARITY = { x | x has odd number of 1s }

- Circuit should evaluate x₁⊕x₂⊕...⊕x<sub>n</sub>

- PARITY in NC1

- PARITY = { x | x has odd number of 1s }

- Circuit should evaluate x₁⊕x₂⊕...⊕x<sub>n</sub>

- Each XOR gate implemented in depth 3

#### PARITY in NC¹

- $PARITY = { x | x has odd number of 1s }$

- Circuit should evaluate x₁⊕x₂⊕...⊕x<sub>n</sub>

- Each XOR gate implemented in depth 3

- - "Boolean" Matrix Multiplication

- - "Boolean" Matrix Multiplication

- $\otimes$  Z=XY:  $z_{ij} = \vee_{k=1..n} (x_{ik} \wedge y_{kj})$

- - "Boolean" Matrix Multiplication

- AC<sup>0</sup> circuit (OR gate with fan-in n, binary AND gates)

- - "Boolean" Matrix Multiplication

- $\otimes$  Z=XY:  $z_{ij} = \vee_{k=1..n} (x_{ik} \wedge y_{kj})$

- a AC<sup>0</sup> circuit (OR gate with fan-in n, binary AND gates)

- If X adjacency matrix (with self-loops), X<sup>t</sup><sub>ij</sub>=1 iff path from i to j of length t or less

- - "Boolean" Matrix Multiplication

- $\otimes$  Z=XY:  $z_{ij} = \vee_{k=1..n} (x_{ik} \wedge y_{kj})$

- AC<sup>0</sup> circuit (OR gate with fan-in n, binary AND gates)

- If X adjacency matrix (with self-loops),  $X^{t}_{ij}$  = 1 iff path from i to j of length t or less

- X<sup>m</sup><sub>ij</sub> for m ≥ n is the transitive closure

- - "Boolean" Matrix Multiplication

- $\otimes$  Z=XY:  $z_{ij} = \vee_{k=1..n} (x_{ik} \wedge y_{kj})$

- AC<sup>0</sup> circuit (OR gate with fan-in n, binary AND gates)

- If X adjacency matrix (with self-loops),  $X^{t}_{ij}$  = 1 iff path from i to j of length t or less

- O(log n) matrix multiplications to compute X<sup>n</sup>ij

- - "Boolean" Matrix Multiplication

- $\otimes$  Z=XY:  $z_{ij} = \vee_{k=1..n} (x_{ik} \wedge y_{kj})$

- AC<sup>0</sup> circuit (OR gate with fan-in n, binary AND gates)

- If X adjacency matrix (with self-loops),  $X^{t}_{ij}$  = 1 iff path from i to j of length t or less

- O(log n) matrix multiplications to compute X<sup>n</sup>ij

- Total depth O(log n)

Generate circuit (implicitly) and evaluate

- Generate circuit (implicitly) and evaluate

- $\circ$  cf. NC  $\subseteq$  P. But now, to conserve space, a recursive evaluation (rather than bottom-up).

- Generate circuit (implicitly) and evaluate

- $\circ$  cf. NC  $\subseteq$  P. But now, to conserve space, a recursive evaluation (rather than bottom-up).

- For each gate, recursively evaluate each input wire

- Generate circuit (implicitly) and evaluate

- cf. NC  $\subseteq$  P. But now, to conserve space, a recursive evaluation (rather than bottom-up).

- For each gate, recursively evaluate each input wire

- Storage: A path to the current node, from the output node: since bounded fan-in, takes O(1) bits per node; since logspace uniform that is sufficient to compute the node id in logspace

- Generate circuit (implicitly) and evaluate

- cf. NC  $\subseteq$  P. But now, to conserve space, a recursive evaluation (rather than bottom-up).

- For each gate, recursively evaluate each input wire

- Storage: A path to the current node, from the output node: since bounded fan-in, takes O(1) bits per node; since logspace uniform that is sufficient to compute the node id in logspace

- And at each node along the path, the input wire values evaluated results so far (again O(1) bits per node)

- Generate circuit (implicitly) and evaluate

- cf. NC  $\subseteq$  P. But now, to conserve space, a recursive evaluation (rather than bottom-up).

- For each gate, recursively evaluate each input wire

- Storage: A path to the current node, from the output node: since bounded fan-in, takes O(1) bits per node; since logspace uniform that is sufficient to compute the node id in logspace

- And at each node along the path, the input wire values evaluated results so far (again O(1) bits per node)

- Length of path = depth of circuit = O(log n)

- Also recall PATH is NL-complete

- Also recall PATH is NL-complete

- with respect to log-space reductions

- Also recall PATH is NL-complete

- with respect to log-space reductions

- o in fact, with respect to NC¹ reductions

- Recall PATH ∈ AC¹

- Also recall PATH is NL-complete

- with respect to log-space reductions

- o in fact, with respect to NC¹ reductions

- For NL machine M, can build (in log-space) an NC<sup>1</sup> circuit which on input x, outputs (i,j)<sup>th</sup> entry of the adjacency matrix of configuration graph of M(x). (Configuration O, the start configuration depends on x.)

- Also recall PATH is NL-complete

- with respect to log-space reductions

- o in fact, with respect to NC¹ reductions

- For NL machine M, can build (in log-space) an NC¹ circuit which on input x, outputs (i,j)<sup>th</sup> entry of the adjacency matrix of configuration graph of M(x). (Configuration O, the start configuration depends on x.)

- Combining the NC¹ circuits for reduction and the AC¹ circuit for PATH, we get an AC¹ circuit

- - $AC^0 ⊆ NC^1$  as  $PARITY ∉ AC^0$  (later)

- Ø Open: whether  $NC^i ⊆ AC^i ⊆ NC^{i+1}$  for larger i

- Ø Open: whether  $NC^i ⊆ AC^i ⊆ NC^{i+1}$  for larger i

- Open: Is NC = P? (Can all polynomial time decidable languages be sped up to poly-log time using parallelization?)

#### Zoo

Recall Uniform circuit family: circuits in the family can be generated by a TM

- Recall Uniform circuit family: circuits in the family can be generated by a TM

- Suppose circuits are super-polynomially large. Cannot be logspace-uniform or P-uniform.

- Recall Uniform circuit family: circuits in the family can be generated by a TM

- Suppose circuits are super-polynomially large. Cannot be logspace-uniform or P-uniform.

- DC uniform allows exponentially large circuits

- Recall Uniform circuit family: circuits in the family can be generated by a TM

- Suppose circuits are super-polynomially large. Cannot be logspace-uniform or P-uniform.

- DC uniform allows exponentially large circuits

- Still requires polynomial time implicit computation of the circuit

- Recall Uniform circuit family: circuits in the family can be generated by a TM

- Suppose circuits are super-polynomially large. Cannot be logspace-uniform or P-uniform.

- DC uniform allows exponentially large circuits

- Still requires polynomial time implicit computation of the circuit

- Coincides with EXP (Why?)

Restricted to constant depth, 2<sup>poly(n)</sup> size, unbounded fan-in DC uniform circuit families decide exactly languages in PH

- Restricted to constant depth, 2<sup>poly(n)</sup> size, unbounded fan-in DC uniform circuit families decide exactly languages in PH

- Given a DC uniform circuit (w.l.o.g alternating levels of AND and OR gates, and NOT gates only at the input level) of depth k, an equivalent quantified expression with k alternations

- Restricted to constant depth, 2<sup>poly(n)</sup> size, unbounded fan-in DC uniform circuit families decide exactly languages in PH

- Given a DC uniform circuit (w.l.o.g alternating levels of AND and OR gates, and NOT gates only at the input level) of depth k, an equivalent quantified expression with k alternations

- Given a quantified expression with k alternations, an equivalent DC uniform circuit of depth k+2

From circuit to quantified expression

- From circuit to quantified expression

- Consider game played on the circuit: adversary picks an input edge to the AND level and Alice picks an input edge to the OR level, going through levels top to bottom

- From circuit to quantified expression

- Consider game played on the circuit: adversary picks an input edge to the AND level and Alice picks an input edge to the OR level, going through levels top to bottom

- Alice wins if adversary "breaks off the path" (by picking either a non-wire edge or a wire not continuing the path), or if the path terminates at literal of value 1 (w/o breaking)

From circuit to quantified expression

Can check in poly time

Consider game played on the circuit: adversary picks an input edge to the AND level and Alice picks an input edge to the OR level, going through levels top to bottom

Alice wins if adversary "breaks off the path" (by picking either a non-wire edge or a wire not continuing the path), or if the path terminates at literal of value 1 (w/o breaking)

From circuit to quantified expression

Can

check in

poly time

Consider game played on the circuit: adversary picks an input edge to the AND level and Alice picks an input edge to the OR level, going through levels top to bottom

- Alice wins if adversary "breaks off the path" (by picking either a non-wire edge or a wire not continuing the path), or if the path terminates at literal of value 1 (w/o breaking)

- Input accepted by the circuit iff Alice has a winning strategy (i.e., if the quantified expression is true)

From circuit to quantified expression

Can check in poly time

Consider game played on the circuit: adversary picks an input edge to the AND level and Alice picks an input edge to the OR level, going through levels top to bottom

- Alice wins if adversary "breaks off the path" (by picking either a non-wire edge or a wire not continuing the path), or if the path terminates at literal of value 1 (w/o breaking)

- Input accepted by the circuit iff Alice has a winning strategy (i.e., if the quantified expression is true)

- Each edge has a polynomially long label, and quantified variables take values from the same domain. Checking if edge is a correct wire in poly time (uniformity)

From quantified expression to circuit:

- From quantified expression to circuit:

- © Circuit has depth-2 sub-circuits evaluating the poly-time condition for each possible assignment of the quantified variables.

- From quantified expression to circuit:

- © Circuit has depth-2 sub-circuits evaluating the poly-time condition for each possible assignment of the quantified variables.

- Hang these sub-circuits at the leaves of a k-level AND-OR tree appropriately

- From quantified expression to circuit:

- © Circuit has depth-2 sub-circuits evaluating the poly-time condition for each possible assignment of the quantified variables.

- Hang these sub-circuits at the leaves of a k-level AND-OR tree appropriately

- © Circuit can be implicitly computed in polynomial time. Size 20(total length of variables)

NC<sup>i</sup> and AC<sup>i</sup>

- NC<sup>i</sup> and AC<sup>i</sup>

- DC-uniform

- NC<sup>i</sup> and AC<sup>i</sup>

- DC-uniform

- PH and EXP

NC<sup>i</sup> and AC<sup>i</sup>

DC-uniform

PH and EXP

Later, more circuits and non-uniform computation (time permitting)

- NC<sup>i</sup> and AC<sup>i</sup>

- DC-uniform

- PH and EXP

- Later, more circuits and non-uniform computation (time permitting)

- PARITY ∉ AC<sup>0</sup>

- NC<sup>i</sup> and AC<sup>i</sup>

- DC-uniform

- PH and EXP

- Later, more circuits and non-uniform computation (time permitting)

- PARITY ∉ AC<sup>0</sup>

- Decision trees, Branching programs

- NC<sup>i</sup> and AC<sup>i</sup>

- DC-uniform

- PH and EXP

- Later, more circuits and non-uniform computation (time permitting)

- PARITY ∉ AC<sup>0</sup>

- Decision trees, Branching programs

- Connections between circuit lowerbounds and other complexity class separations