Lecture 24 Weak circuits are indeed weak

Today:

- Today:

- Today:

- - Two different proofs! (Latter generalizes to ACC<sup>0</sup>)

- Today:

- - Two different proofs! (Latter generalizes to ACC<sup>0</sup>)

- CLIQUE cannot be decided by poly-sized monotone circuits

- Today:

- - Two different proofs! (Latter generalizes to ACC<sup>o</sup>)

- CLIQUE cannot be decided by poly-sized monotone circuits

- Only sketches/partial proofs. See textbook or lecturenotes from linked courses)

# PARITY ∉ AC<sup>0</sup>

## PARITY $\oplus$ AC<sup>0</sup>

Recall ACO

### PARITY ACO

- Recall ACO

- Poly size, constant depth (unbounded fan-in)

### PARITY ACO

- Recall ACO

- Poly size, constant depth (unbounded fan-in)

- Today, non-uniform AC<sup>0</sup>

#### PARITY # ACO

- Recall AC<sup>0</sup>

- Poly size, constant depth (unbounded fan-in)

- Today, non-uniform AC<sup>0</sup>

- How powerful can AC<sup>0</sup> be?

#### PARITY # ACO

- Recall AC<sup>0</sup>

- Poly size, constant depth (unbounded fan-in)

- Today, non-uniform AC<sup>0</sup>

- How powerful can AC<sup>0</sup> be?

- Recall PARITY

#### PARITY ∉ AC<sup>0</sup>

- Recall AC<sup>0</sup>

- Poly size, constant depth (unbounded fan-in)

- Today, non-uniform AC<sup>0</sup>

- How powerful can AC<sup>0</sup> be?

- Recall PARITY

- How shallow can a poly-sized circuit family for PARITY be?

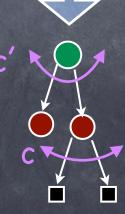

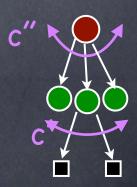

Suppose constant depth (say ≤ d, d being minimal) circuits for PARITY

- Suppose constant depth (say ≤ d, d being minimal) circuits for PARITY

- Plan for contradiction: Show depth d-1 circuits for every input size n: start from depth d circuit for a larger n', and construct one for the smaller n.

- Suppose constant depth (say ≤ d, d being minimal) circuits for PARITY

- Plan for contradiction: Show depth d-1 circuits for every input size n: start from depth d circuit for a larger n', and construct one for the smaller n.

- By "restricting" to n inputs

- Suppose constant depth (say ≤ d, d being minimal) circuits for PARITY

- Plan for contradiction: Show depth d-1 circuits for every input size n: start from depth d circuit for a larger n', and construct one for the smaller n.

- By "restricting" to n inputs

- And showing how to rewrite with depth d-1, staying poly sized

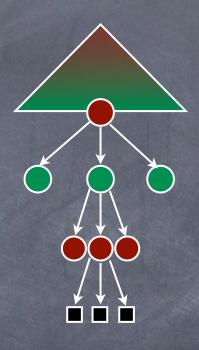

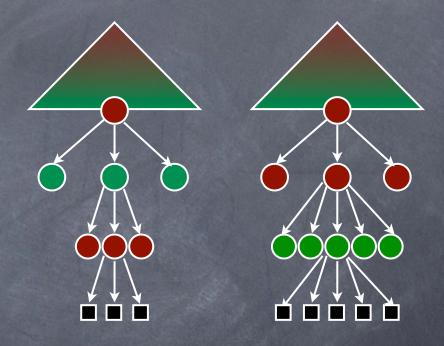

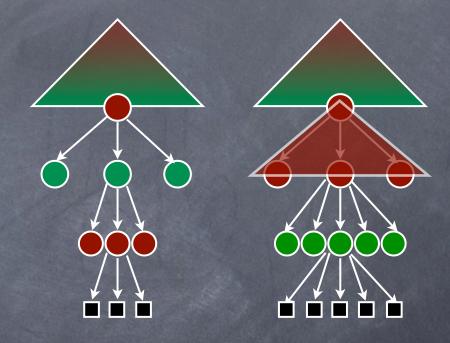

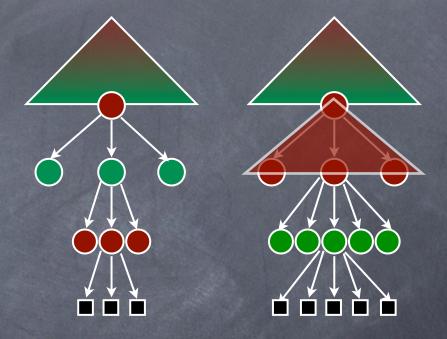

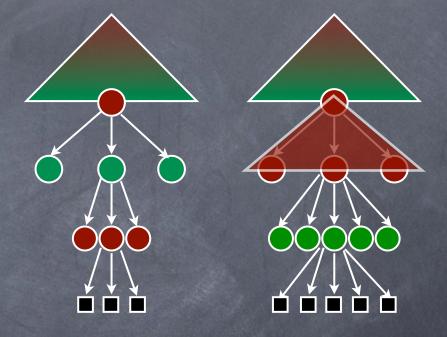

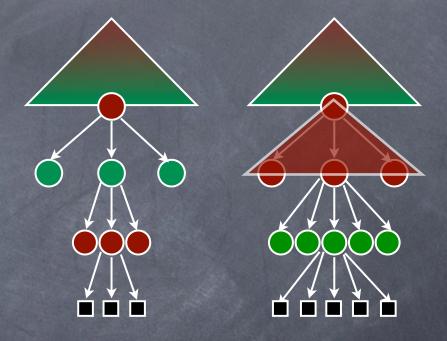

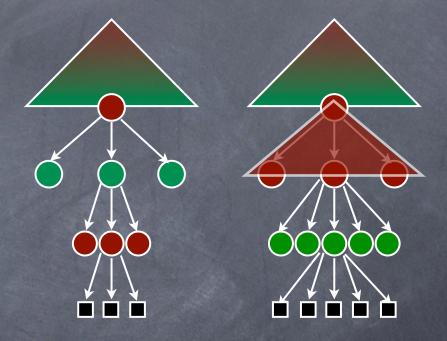

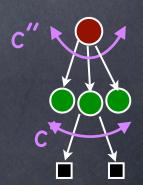

Any function can be written as depth 2 AND-OR tree or an OR-AND tree

- Any function can be written as depth 2 AND-OR tree or an OR-AND tree

- But exponential size

- Any function can be written as depth 2 AND-OR tree or an OR-AND tree

- But exponential size

- Any circuit can be rewritten as an AND-OR tree (each leaf has a literal, possibly shared with other leaves)

- Any function can be written as depth 2 AND-OR tree or an OR-AND tree

- But exponential size

- Any circuit can be rewritten as an AND-OR tree (each leaf has a literal, possibly shared with other leaves)

- If polynomial size and constant depth (AC<sup>0</sup>), stays so

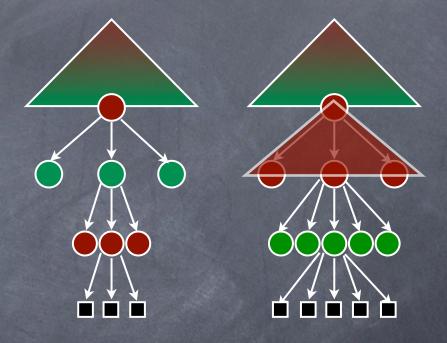

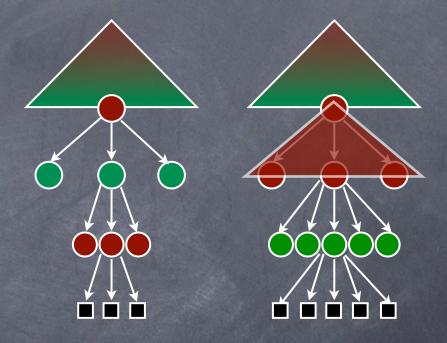

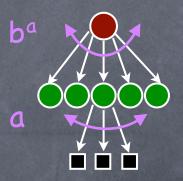

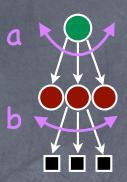

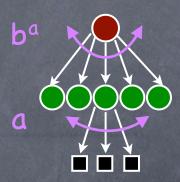

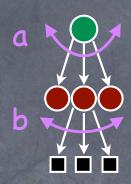

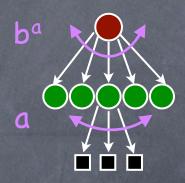

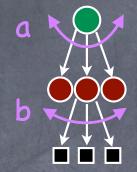

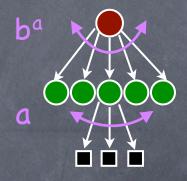

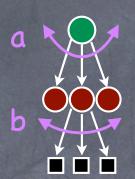

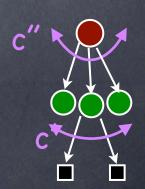

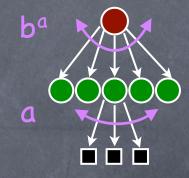

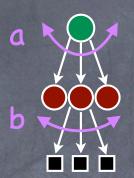

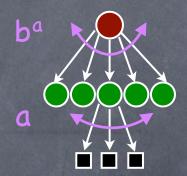

In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- Distributivity

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- Distributivity

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- Distributivity

#### Switching

- In an AND-OR tree, if bottom two levels can be replaced by equivalent two levels with switched AND-OR order, and polynomial size

- A depth d AC<sup>0</sup> circuit

changes into depth d-1

- When is switching possible?

- Distributivity

- But may increase size to exponential

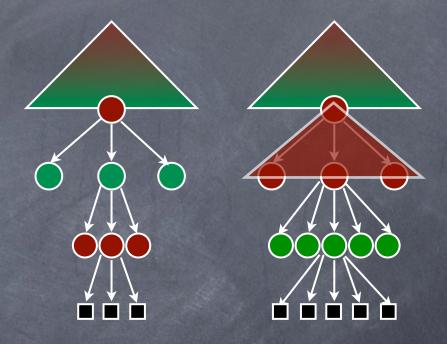

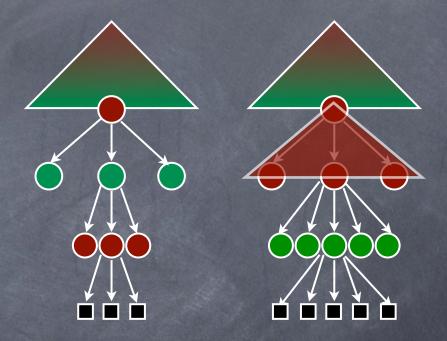

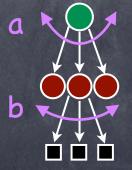

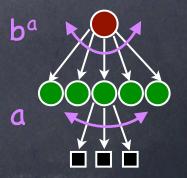

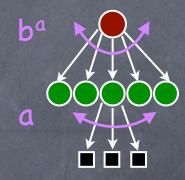

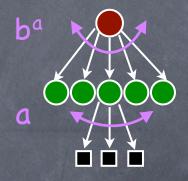

A modified function has a switched circuit

- A modified function has a switched circuit

- Size stays polynomial even after switching

- A modified function has a switched circuit

- Size stays polynomial even after switching

© Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- A modified function has a switched circuit

- Size stays polynomial even after switching

- © Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- A modified function has a switched circuit

- Size stays polynomial even after switching

- © Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- A modified function has a switched circuit

- Size stays polynomial even after switching

- © Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- Still function of many variables

- A modified function has a switched circuit

- Size stays polynomial even after switching

- © Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- Still function of many variables

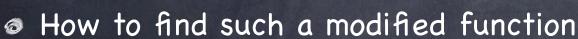

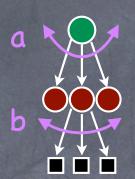

- How to find such a modified function

- A modified function has a switched circuit

- Size stays polynomial even after switching

- Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- Still function of many variables

Random restriction

- A modified function has a switched circuit

- Size stays polynomial even after switching

- © Computes same function as before but with most variables already set to specific values (a "restriction" of the original function)

- Still function of many variables

- How to find such a modified function

- 10W 10 IIIIa sacii a illoaillea faliciloii

Random restriction

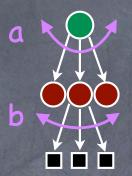

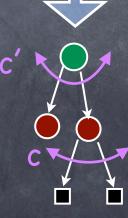

Random restriction. With positive probability:

- Random restriction. With positive probability:

- can switch bottom levels, staying poly sized

- Random restriction. With positive probability:

- can switch bottom levels, staying poly sized

- with high probability for each node above the leaf level (switching lemma); then union bound

- Random restriction. With positive probability:

- can switch bottom levels, staying poly sized

- with high probability for each node above the leaf level (switching lemma); then union bound

- computes PARITY for n<sup>2/3</sup> variables (Chernoff)

- Random restriction. With positive probability:

- can switch bottom levels, staying poly sized

- with high probability for each node above the leaf level (switching lemma); then union bound

- computes PARITY for n<sup>2/3</sup> variables (Chernoff)

- Depth d-1, poly-sized circuit family for PARITY

- Random restriction. With positive probability:

- can switch bottom levels, staying poly sized

- with high probability for each node above the leaf level (switching lemma); then union bound

- computes PARITY for n<sup>2/3</sup> variables (Chernoff)

- Depth d-1, poly-sized circuit family for PARITY

- Contradiction: started with minimal depth!

- - Generalizes to ACC<sup>0</sup>(p) for odd primes p

- - Generalizes to ACC<sup>0</sup>(p) for odd primes p

- Plan:

- - Generalizes to ACC<sup>0</sup>(p) for odd primes p

- Plan:

- Given a circuit C, can find a polynomial s.t.

- - Generalizes to ACC<sup>0</sup>(p) for odd primes p

- Plan:

- Given a circuit C, can find a polynomial s.t.

- Polynomial has "low degree"

- - Generalizes to ACC<sup>0</sup>(p) for odd primes p

- Plan:

- Given a circuit C, can find a polynomial s.t.

- Polynomial has "low degree"

- Polynomial agrees with C on most inputs

- - Generalizes to ACC<sup>0</sup>(p) for odd primes p

- Plan:

- Given a circuit C, can find a polynomial s.t.

- Polynomial has "low degree"

- Polynomial agrees with C on most inputs

- Show that no low degree polynomial can agree with PARITY on that many inputs

Assume circuit has OR, NOT gates

- Assume circuit has OR, NOT gates

- Replace gates by polynomials (over some field), and compose together into one big polynomial

- Assume circuit has OR, NOT gates

- Replace gates by polynomials (over some field), and compose together into one big polynomial

- If we do this faithfully, degree will be large

- Assume circuit has OR, NOT gates

- Replace gates by polynomials (over some field), and compose together into one big polynomial

- If we do this faithfully, degree will be large

- Large enough to evaluate PARITY

- Assume circuit has OR, NOT gates

- Replace gates by polynomials (over some field), and compose together into one big polynomial

- If we do this faithfully, degree will be large

- Large enough to evaluate PARITY

- So allow polynomials which err on some inputs

- Assume circuit has OR, NOT gates

- Replace gates by polynomials (over some field), and compose together into one big polynomial

- If we do this faithfully, degree will be large

- Large enough to evaluate PARITY

- So allow polynomials which err on some inputs

- At each gate will pick polynomial from a distribution

- Assume circuit has OR, NOT gates

- Replace gates by polynomials (over some field), and compose together into one big polynomial

- If we do this faithfully, degree will be large

- Large enough to evaluate PARITY

- So allow polynomials which err on some inputs

- At each gate will pick polynomial from a distribution

- Composed polynomial will be good with prob. > 0

# Polynomials for OR, NOT and PARITY

# Polynomials for OR, NOT and PARITY

Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- If over GF(2), PARITY is just sum (degree 1)!

- Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- If over GF(2), PARITY is just sum (degree 1)!

- We will work over GF(q), q>2

- Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- If over GF(2), PARITY is just sum (degree 1)!

- We will work over GF(q), q>2

- $\bigcirc$  PARITY =  $[1-(1-2x_1)(1-2x_2)...(1-2x_n)]/2$  (if  $2\neq 0$ )

- Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- If over GF(2), PARITY is just sum (degree 1)!

- We will work over GF(q), q>2

- PARITY =  $[1-(1-2x_1)(1-2x_2)....(1-2x_n)]/2$  (if 2≠0)

- NOT = 1-x.

- Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- If over GF(2), PARITY is just sum (degree 1)!

- We will work over GF(q), q>2

- PARITY =  $[1-(1-2x_1)(1-2x_2)....(1-2x_n)]/2$  (if 2≠0)

- NOT = 1-x.

- $\odot$  OR = 1- (1- $x_1$ )...(1- $x_n$ )

- Want that PARITY is complex (high degree) while OR, NOT are simple (low degree)

- If over GF(2), PARITY is just sum (degree 1)!

- We will work over GF(q), q>2

- PARITY =  $[1-(1-2x_1)(1-2x_2)....(1-2x_n)]/2$  (if 2≠0)

- NOT = 1-x.

- $\odot$  OR = 1- (1- $x_1$ )...(1- $x_n$ )

- But high degree! Need OR to be simple!

© Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- © Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- If  $OR(x_1,...,x_n)=0$  then  $p(x_1,...,x_n)=0$

- © Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- If  $OR(x_1,...,x_n)=0$  then  $p(x_1,...,x_n)=0$

- © Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- If  $OR(x_1,...,x_n)=0$  then  $p(x_1,...,x_n)=0$

- If  $OR(x_1,...,x_n)=1$

- $\circ$   $Pr_a[a_1x_1 + ... + a_nx_n = 0] \le 1/q$  (why?)

- © Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- If  $OR(x_1,...,x_n)=0$  then  $p(x_1,...,x_n)=0$

- If  $OR(x_1,...,x_n)=1$

- $\circ$   $Pr_a[a_1x_1 + ... + a_nx_n = 0] \le 1/q$  (why?)

- Recall in GF(q),  $u^{q-1} = 1$  unless u=0 (since non-0 elements form a group of order q-1 under multiplication)

- © Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- If  $OR(x_1,...,x_n)=0$  then  $p(x_1,...,x_n)=0$

- If  $OR(x_1,...,x_n)=1$

- $\circ$   $Pr_a[a_1x_1 + ... + a_nx_n = 0] \le 1/q$  (why?)

- Recall in GF(q),  $u^{q-1} = 1$  unless u=0 (since non-0 elements form a group of order q-1 under multiplication)

- $\circ$  i.e.  $Pr_a[(a_1x_1 + ... + a_nx_n)^{q-1} = 1] \ge 1-1/q$

- © Consider (random) polynomial  $p(x_1,...,x_n) = (a_1x_1 + ... + a_nx_n)^{q-1}$ where  $a_i$  are picked at random from the field

- If  $OR(x_1,...,x_n)=0$  then  $p(x_1,...,x_n)=0$

- $\circ$  If  $OR(x_1,...,x_n)=1$

- $\circ$   $Pr_a[a_1x_1 + ... + a_nx_n = 0] \le 1/q$  (why?)

- Recall in GF(q),  $u^{q-1} = 1$  unless u=0 (since non-0 elements form a group of order q-1 under multiplication)

- $\circ$  i.e.  $Pr_a[(a_1x_1 + ... + a_nx_n)^{q-1} = 1] \ge 1-1/q$

- Can boost probability by doing (exact) OR t times: deg < qt</p>

Ø OR: a random polynomial of degree  $O(\log 1/\epsilon)$ , such that it is correct with prob. > 1-€

- Ø OR: a random polynomial of degree  $O(\log 1/\epsilon)$ , such that it is correct with prob. > 1-€

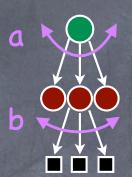

- Composing gate-polynomials into circuit-polynomial

- Ø OR: a random polynomial of degree  $O(\log 1/\epsilon)$ , such that it is correct with prob. > 1-€

- Composing gate-polynomials into circuit-polynomial

- Substitute child polynomials as variables

- Ø OR: a random polynomial of degree  $O(\log 1/\epsilon)$ , such that it is correct with prob. > 1-€

- Composing gate-polynomials into circuit-polynomial

- Substitute child polynomials as variables

- Degree multiplies: depth d circuit gives deg ○(log 1/∈)<sup>d</sup>

- Ø OR: a random polynomial of degree O(log 1/∈), such that it is correct with prob. > 1-€

- Composing gate-polynomials into circuit-polynomial

- Substitute child polynomials as variables

- Tegree multiplies: depth d circuit gives deg  $O(\log 1/\epsilon)^d$

- Ø OR: a random polynomial of degree  $O(\log 1/\epsilon)$ , such that it is correct with prob. > 1-€

- Composing gate-polynomials into circuit-polynomial

- Substitute child polynomials as variables

- $\odot$  Degree multiplies: depth d circuit gives deg  $O(\log 1/\epsilon)^d$

- Error adds (by union bound): size s circuit gives error < se</p>

- Ø OR: a random polynomial of degree O(log 1/∈), such that it is correct with prob. > 1-€

- Composing gate-polynomials into circuit-polynomial

- Substitute child polynomials as variables

- $\odot$  Degree multiplies: depth d circuit gives deg  $O(\log 1/\epsilon)^d$

- Sing ∈=1/(4s), degree  $O(\log s)^d$  polynomial, correct w.p. > 3/4

- One polynomial, correct on > 3/4 fraction of inputs (why?)

© Can PARITY also be approximated (i.e., calculated for some large input set S) by a low-degree polynomial?

- © Can PARITY also be approximated (i.e., calculated for some large input set S) by a low-degree polynomial?

- PARITY is essentially  $\Pi_{i=1 \text{ to } n}$  x<sub>i</sub>, for inputs from {+1,−1}<sup>n</sup>

- Can PARITY also be approximated (i.e., calculated for some large input set S) by a low-degree polynomial?

- PARITY is essentially Π<sub>i=1</sub> to n x<sub>i</sub>, for inputs from  $\{+1,-1\}<sup>n</sup>$

- If can calculate  $\Pi_{i=1 \text{ to } n}$   $x_i$  (for  $S \subseteq \{+1,-1\}^n$ ) using degree D, then can calculate (for S) any polynomial using degree D+n/2 polynomial (why?)

- Can PARITY also be approximated (i.e., calculated for some large input set S) by a low-degree polynomial?

- PARITY is essentially Π<sub>i=1</sub> to n x<sub>i</sub>, for inputs from  $\{+1,-1\}<sup>n</sup>$

- If can calculate  $\Pi_{i=1 \text{ to } n}$   $x_i$  (for  $S \subseteq \{+1,-1\}^n$ ) using degree D, then can calculate (for S) any polynomial using degree D+n/2 polynomial (why?)

- But if S large, too many polynomials, distinct for S

- Can PARITY also be approximated (i.e., calculated for some large input set S) by a low-degree polynomial?

- PARITY is essentially Π<sub>i=1</sub> to n x<sub>i</sub>, for inputs from  $\{+1,-1\}<sup>n</sup>$

- If can calculate  $\Pi_{i=1 \text{ to } n}$   $x_i$  (for  $S \subseteq \{+1,-1\}^n$ ) using degree D, then can calculate (for S) any polynomial using degree D+n/2 polynomial (why?)

- But if S large, too many polynomials, distinct for S

- Need D =  $\Omega(\sqrt{n})$  to have enough degree D+n/2 polys.

Given depth d, size s circuit C, there is a polynomial of degree O(log(s))<sup>d</sup> which agrees with C on 3/4 of inputs

- Given depth d, size s circuit C, there is a polynomial of degree O(log(s))<sup>d</sup> which agrees with C on 3/4 of inputs

- Using approximate OR polynomials

- Given depth d, size s circuit C, there is a polynomial of degree O(log(s))<sup>d</sup> which agrees with C on 3/4 of inputs

- Using approximate OR polynomials

- The Even if circuit has  $Mod_q$  (boolean) gates:  $(x_1+...+x_n)^{q-1}$

- Given depth d, size s circuit C, there is a polynomial of degree O(log(s))<sup>d</sup> which agrees with C on 3/4 of inputs

- Using approximate OR polynomials

- The Even if circuit has  $Mod_q$  (boolean) gates:  $(x_1+...+x_n)^{q-1}$

- $\circ$  PARITY needs degree  $\Omega(\sqrt{n})$  polynomial for approximation

- Given depth d, size s circuit C, there is a polynomial of degree O(log(s))<sup>d</sup> which agrees with C on 3/4 of inputs

- Using approximate OR polynomials

- The Even if circuit has  $Mod_q$  (boolean) gates:  $(x_1+...+x_n)^{q-1}$

- $\circ$  PARITY needs degree  $\Omega(\sqrt{n})$  polynomial for approximation

- log(s) =  $\Omega(\sqrt{n})^{1/d}$  or s =  $2^{\Omega(n)^{n}(1/2d)}$ : i.e., if depth is constant then size not poly (in fact exponential)

### Monotone Circuits

#### Monotone Circuits

Another restricted class for which strong lower-bounds are known

- Another restricted class for which strong lower-bounds are known

- Monotone circuits: no NOT gate (and no neg. literal)

- Another restricted class for which strong lower-bounds are known

- Monotone circuits: no NOT gate (and no neg. literal)

- For monotonic functions f

- Another restricted class for which strong lower-bounds are known

- Monotone circuits: no NOT gate (and no neg. literal)

- For monotonic functions f

- To show that f has no poly-sized monotone circuit family

- Another restricted class for which strong lower-bounds are known

- Monotone circuits: no NOT gate (and no neg. literal)

- For monotonic functions f

- To show that f has no poly-sized monotone circuit family

- Still possible that f may have a more efficient nonmonotone circuit family (or even be in P)

© CLIQUE<sub>n,k</sub> does not have poly-sized monotone circuits

- CLIQUEn,k does not have poly-sized monotone circuits

- A way to turn a circuit into an approximately correct circuit, gate by gate (AND/OR gate → "approximation gate")

- CLIQUE<sub>n,k</sub> does not have poly-sized monotone circuits

- A way to turn a circuit into an approximately correct circuit, gate by gate (AND/OR gate → "approximation gate")

- Will consider effect of this change on some Yes examples and some No examples

- CLIQUE<sub>n,k</sub> does not have poly-sized monotone circuits

- A way to turn a circuit into an approximately correct circuit, gate by gate (AND/OR gate → "approximation gate")

- Will consider effect of this change on some Yes examples and some No examples

- Converting each gate to approximation makes only a few extra examples go wrong

- CLIQUEn,k does not have poly-sized monotone circuits

- A way to turn a circuit into an approximately correct circuit, gate by gate (AND/OR gate → "approximation gate")

- Will consider effect of this change on some Yes examples and some No examples

- Converting each gate to approximation makes only a few extra examples go wrong

- A circuit with only approximation gates errs on a large number of the examples

- CLIQUE<sub>n,k</sub> does not have poly-sized monotone circuits

- A way to turn a circuit into an approximately correct circuit, gate by gate (AND/OR gate → "approximation gate")

- Will consider effect of this change on some Yes examples and some No examples

- Converting each gate to approximation makes only a few extra examples go wrong

- A circuit with only approximation gates errs on a large number of the examples

- Original circuit must have been large

Input sets

- Input sets

- Yes set: graphs with no edges except a single k-clique.

No set: complete (k-1)-partite graphs

- Input sets

- Yes set: graphs with no edges except a single k-clique. No set: complete (k-1)-partite graphs

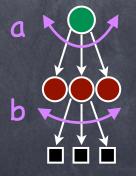

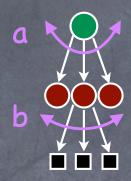

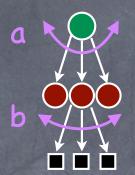

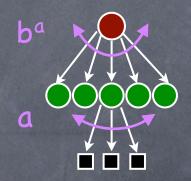

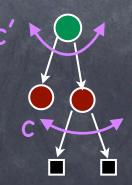

- Since monotone circuit, we can label each gate with a set of subgraphs which will make the gate's output 1

- Input sets

- Yes set: graphs with no edges except a single k-clique. No set: complete (k-1)-partite graphs

- Since monotone circuit, we can label each gate with a set of subgraphs which will make the gate's output 1

- Input gates: edges

- Input sets

- Yes set: graphs with no edges except a single k-clique. No set: complete (k-1)-partite graphs

- Since monotone circuit, we can label each gate with a set of subgraphs which will make the gate's output 1

- Input gates: edges

- OR: take union of the two sets of input-subsets

- Input sets

- Yes set: graphs with no edges except a single k-clique. No set: complete (k-1)-partite graphs

- Since monotone circuit, we can label each gate with a set of subgraphs which will make the gate's output 1

- Input gates: edges

- OR: take union of the two sets of input-subsets

- AND: take set of pair-wise unions of input-subsets

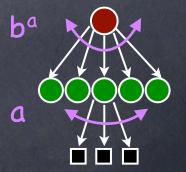

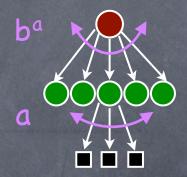

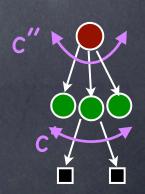

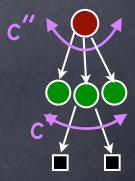

Approximation gate: output wire labeled by a sample of M cliques of at most t vertices. Value 1 if at least one of those M cliques is present in the input

- Approximation gate: output wire labeled by a sample of M cliques of at most t vertices. Value 1 if at least one of those M cliques is present in the input

- Input gates: edges

- Approximation gate: output wire labeled by a sample of M cliques of at most t vertices. Value 1 if at least one of those M cliques is present in the input

- Input gates: edges

- OR: take union of the two sets of subsets, and "prune" to M subsets

- Approximation gate: output wire labeled by a sample of M cliques of at most t vertices. Value 1 if at least one of those M cliques is present in the input

- Input gates: edges

- OR: take union of the two sets of subsets, and "prune" to M subsets

- AND: take set of pair-wise unions of subsets which are at most t vertices, and "prune" to M subsets

- Approximation gate: output wire labeled by a sample of M cliques of at most t vertices. Value 1 if at least one of those M cliques is present in the input

- Input gates: edges

- OR: take union of the two sets of subsets, and "prune" to M subsets

- AND: take set of pair-wise unions of subsets which are at most t vertices, and "prune" to M subsets

- Pruning uses "sunflower lemma": find a sunflower and replace petals by core

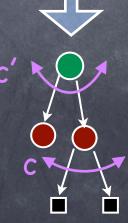

Converting each gate to approximation makes only a few more examples go wrong

- Converting each gate to approximation makes only a few more examples go wrong

- Bounding new false positives among No sets and false negatives among Yes sets introduced by pruning

- Converting each gate to approximation makes only a few more examples go wrong

- Bounding new false positives among No sets and false negatives among Yes sets introduced by pruning

- A circuit with only approximation gates errs on a large number of the examples

- Converting each gate to approximation makes only a few more examples go wrong

- Bounding new false positives among No sets and false negatives among Yes sets introduced by pruning

- A circuit with only approximation gates errs on a large number of the examples

- If output identically "No" then errs on entire Yes set.

Else, output wire's label has some subset X, |X| ≤ t = O(√k),

and then a constant fraction of No-examples get accepted