## LECTURE 24: RUZZO'S THEOREM

Date: November 16, 2023.

All NOT gates are only applied to input

**Boolean Circuits:** A Boolean circuit C with n inputs is a directed acyclic graph with n vertices of in-degree 0, a single vertex of out-degree 0, and whose internal vertices are all labeled with  $\land$ ,  $\lor$ , or  $\neg$ . A vertex labeled with  $\land$ ,  $\lor$ , or  $\neg$  computes the logical and, or, or negation of its inputs, respectively. We assume that vertices labeled with  $\land$  or  $\lor$  have two children and vertices labeled with  $\neg$  have one child. On input  $x \in \{0,1\}^n$ , the output of C is given by the value of the vertex of out-degree 0 and is denoted by C(x).

The size of C is the number of gates in C. The depth of C is the length of the longest path from an input vertex to the output vertex.

Solving Problems using Families of Circuits: A family of circuits  $\{C_n\}_{n\in\mathbb{N}}$  of size S(n) is a collection of Boolean circuits where for all n,  $C_n$  has n inputs and size at most S(n). A language L is in SIZE(S(n)) if there is a family of Boolean circuits  $\{C_n\}_{n\in\mathbb{N}}$  of size S(n) such that for all  $x\in\{0,1\}^n$ ,  $x\in L$  iff  $C_n(x)=1$ .

Uniform Circuit Classes: A family of Boolean circuits  $\{C_n\}_{n\in\mathbb{N}}$  is logspace-uniform if there is a logspace-bounded Turing machine that outputs the circuit  $C_n$  on input  $0^n$ .  $\rightarrow$  0 years of the gradient of the edges.

NC: A language L is in NC<sup>i</sup> if there exists a logspace uniform family of circuits  $\{C_n\}_{n\in\mathbb{N}}$  where  $C_n$  has poly(n) size,  $O((\log n)^i)$  depth, and for all  $x \in \{0,1\}^n$ ,  $x \in L$  iff  $C_n(x) = 1$ .

$$NC = \bigcup_{i \geq 0} NC^i$$

.

**Proposition 1.** Let A and B be  $n \times n$  Boolean matrices. There is a logspace-uniform circuit family of poly(n) size and  $O(\log n)$  depth that computes the Boolean matrix product AB.

Reflexive and Transitive Relations: Recall that a relation on a set S is a set  $R \subseteq S \times S$ . We say R is reflexive if for all  $a \in S$ , we have  $(a, a) \in R$ . We say R is transitive if for all  $a, b, c \in S$ ,  $(a, b) \in R$  and  $(b, c) \in R$  implies  $(a, c) \in R$ .

Reflexive-Transitive Closure: The reflexive transitive closure  $R^*$  of R is the smallest reflexive and transitive relation containing R. Alternatively, if  $R^{\dagger}$  is a reflexive transitive relation and  $R \subseteq R^{\dagger}$ , then  $R^* \subseteq R^{\dagger}$ .

**Proposition 2.** Let S be a set of size n and let  $R \subseteq S \times S$  be a relation on S. There exists a logspace-uniform circuit family of poly(n) size and  $O(\log^2 n)$  depth that computes the reflexive transitive closure  $R^*$  of R.

Bounding Time, Space, and Alternations: The class STA(S(n), T(n), A(n)) is the class of all languages accepted by a Turing machine which is simultaneously S(n)-space-bounded, T(n)-time-bounded, and uses at most A(n) alternations. A \* in a slot means no bound is imposed on that resource. We write  $\Sigma A(n)$  or  $\Pi A(n)$  to indicate that the alternations should start with  $\vee$  or  $\wedge$ , respectively.

Convention: O-alternations - ATM is deterministic

We can establish the following relations.

```

NL = STA (log n, *, Zi)

L = STA(\log n, *, 0)

≤ STA(logn, *, (logn)oti))

NL = STA(\log n, *, \Sigma 1)

P = STA(\log n, *, *) = STA(*, n^{O(1)}, 0)

NP = STA(*, n^{O(1)}, \Sigma 1)

SSTA(bgn, *, *)

\Sigma_k^{\mathsf{p}} = \mathrm{STA}(*, n^{O(1)}, \Sigma k)

\Pi_k^{\mathsf{p}} = \mathrm{STA}(*, n^{O(1)}, \Pi k)

PSPACE = STA(*, n^{O(1)}, *) = STA(n^{O(1)}, *, 0)

NL G NG GP

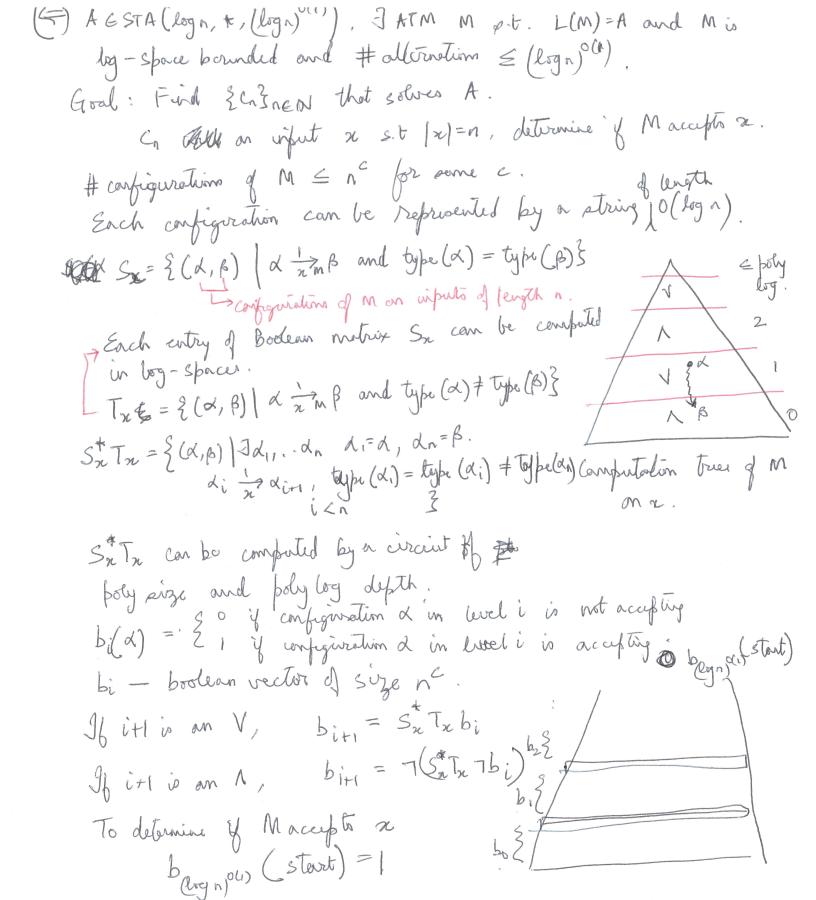

Theorem 3 (Ruzzo '81). NC = STA(\log n, *, (\log n)^{O(1)}).

(=) AENC. I {Cn3nein where size(Cn) \left\( \text{boly}(n)\) and difth (Cn) \left\( \text{frly(lign})\)

and Ecn3ner polices A. and Ecn3 is logspace uniform

Good: Find ATM M that solves A.

Gwen 2

-> Computing C/21(2)

Assume & Reduced to computing value of gate of Gin on input se.

- Name of gate d is binary string of length O(log n)

(Stored logspace).

- Compute the type of gate d -> Run the logspore

TM that computes Cini.

(a) If d is an input gate then value is the appropriate

Spore ruded

= memory to

remember d

bit q e.

(b) If d is a NOT gate then find the input wire to d

and flip the appropriate bit of x.

memory to

(c) If die 1 gate (V gate) then we find the two

run TM

incoming wires into die, (c,d), (c',d)

then using 1-branching (V-branching) compute

& value of c and value of c'.

# atternations = depth (Cn) \le \text{foly(log n)}

```